This video contains a narration followed by a demo, complete with clicking.

(2:00 minutes runtime)

Video Tutorial

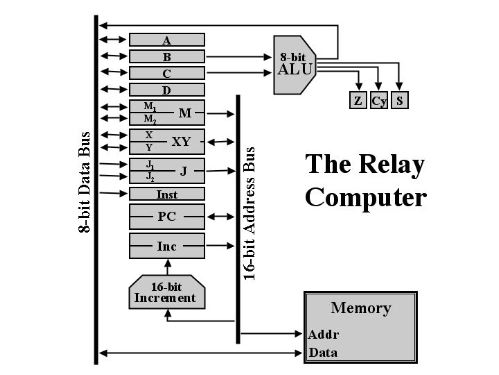

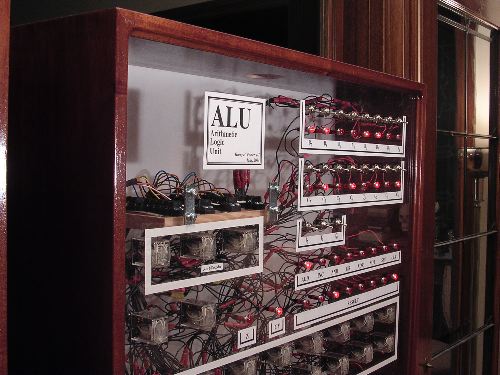

For a video presentation describing the machine in depth, click here (to intro page).Features of the Arithmetic Logic Unit:

Two 8-bit inputs (from B and C registers)

8-bit result (onto data bus)

3-bit function code input

Functions: Add, Increment, And, Or, Xor, Not, Shift-left, Nop

Carry output (from Add, Increment)

Zero-detect output

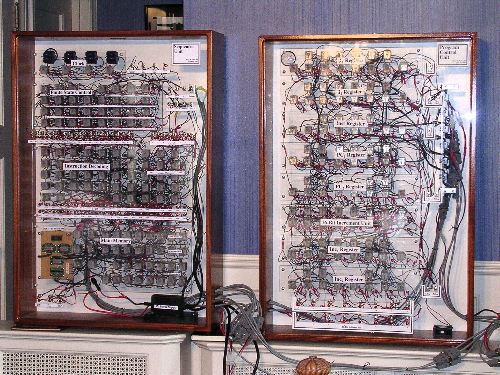

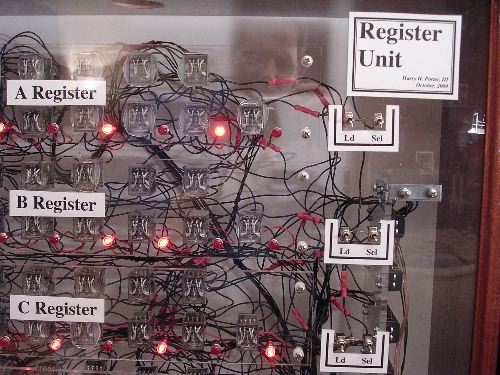

Features of the Register Unit:

8 Registers (8-bits each)

Register Names: A, B, C, D, M1, M2, X, and Y

Data Bus (8 LEDs and 8 Switches)

Features of the Program Control Unit:

Program Counter (16 bits)

Instruction Register (8 bits)

Jump Target Register (16 bits)

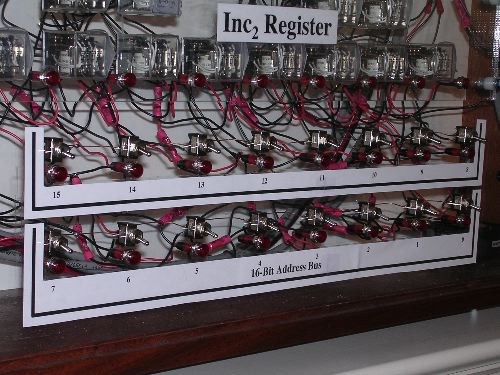

Increment Unit (16 bits)

Increment Register (16 bits)

Address Bus (16 LEDs and 16 Switches)

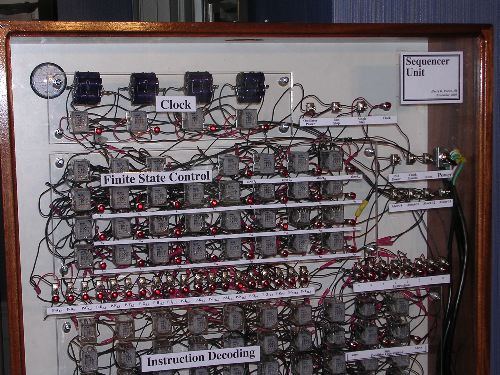

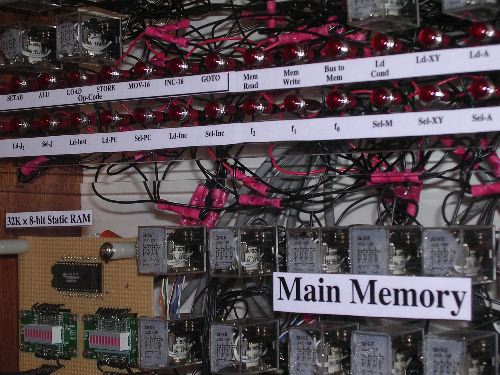

Features of the Sequencer Unit:

Clock (Using capacitors for delay)

Finite State Control (24 states)

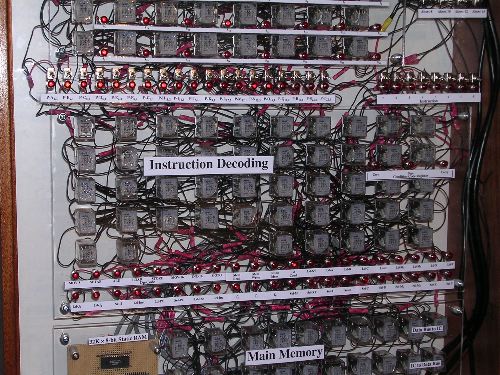

Instruction Decoding

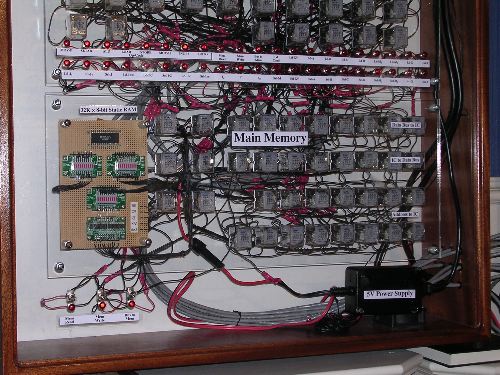

Main Memory (32K x 8bits, static RAM chip)

General Features:

Data Bus (8 bits)

Address Bus (16-bits)

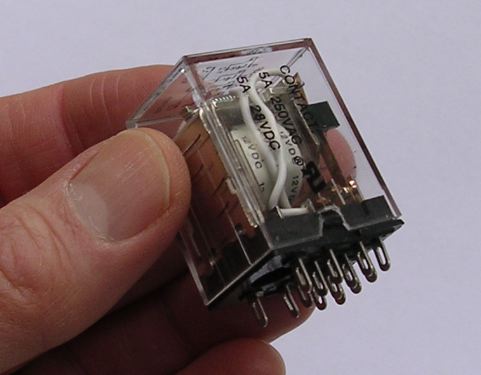

All relays are the identical part (Four-Pole-Double-Throw, 12 Volts)

415 Relays

111 Switches

350 LEDs

Max Power Consumption: Estimated 12 Amps @ 13.5 Volts (160 Watts)

More Info

For more information, click here (Last updated, 17 November 2009: Circuit diagrams added)Video Tutorial

For an in-depth video presentation describing the design of machine, click here (to intro page).

About the Author

Harry H. Porter III, Ph.D.

Computer Science Department

Portland State University

Back to Harry's homepage: click here

Short Bio of Harry: click here

Back to Relay Computer, main page: www.cs.pdx.edu/~harry/Relay

Send email to Harry: harry@cs.pdx.edu

More Photos

Click on any photo for an enlargement.