1. Problem description

Find the minimum number of an array of 8 numbers and return the position and the number. Please refer to homework 1 for a more detailed description. The difference between homework 1 and 2 are:

- HW 2 is comparing 8 numbers

- HW 2 returns the position closest the center position if there are numbers that are equal.

- There is no enable or clock input in HW2. This block is a comparer so it has no need for either.

The goal of this homework is to compare the synthesis of optimization for time and area and do a place and route.

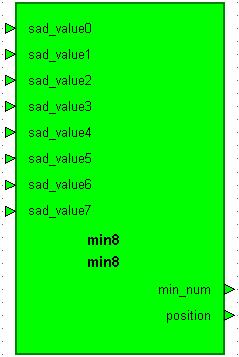

Figure 1. Block diagram of Homework 2.

2. Synthesis with

Conclusion

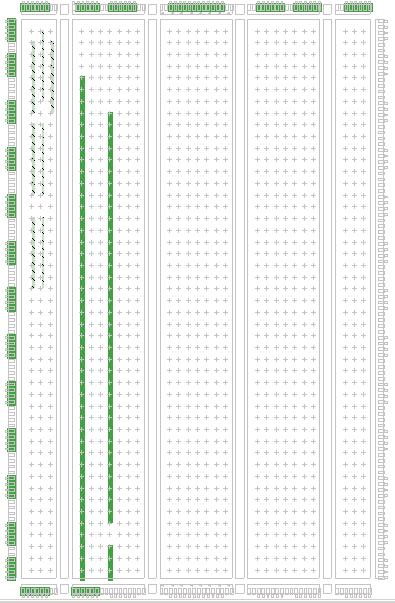

The tools used were Leonardo Spectrum for synthesis and the Xilinx Webpack for place and route. In all scenarios the resource that is filled to capacity first are the IO blocks. While this simple design uses only 5% of the internal resources of the chip, it uses 55% of the IO blocks. This is shown in the place and route section of this report.

When optimizing for delay, the Xilinx tool reported 6 more slices and a slightly higher delay of about 0.01 ns. This is really strange since one would expect the tool to report a significantly shortened delay with slightly higher slice count. I think this is because there is not a lot of circuitry inside the chip, so the delay is really dependent on the IO.

2.1 Optimization

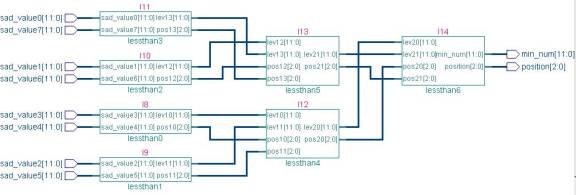

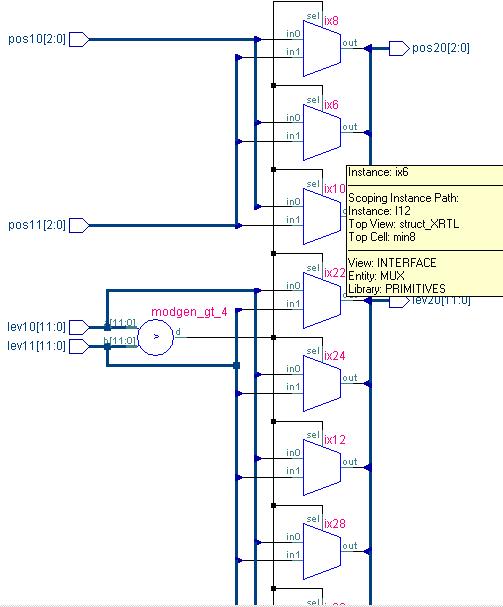

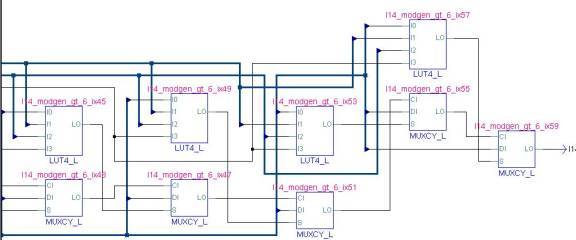

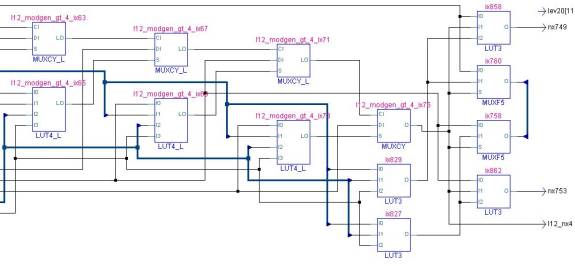

Figure 2 shows the high level synthesis picture and figure 3 shows a gate level design of each block. Each block is a series of mux’s with the selector being the “lessthan” output of the two SAD values. The block level synthesis is shown in figure 4. Notice that it uses lookup tables (LUT) and mux’. The diagram is slightly different when optimizing for delay. This is shown in figure 5.

Figure 2. High level synthesis

Figure 3. Gate level synthesis

Figure 4. Block level synthesis when optimizing for area

Figure 5. Block level synthesis when optimizing for delay

3. Place and Route

The chip used was a Xilinx Virtex II 250. Other pertinent information can be obtained from either the Xilinx web site or the “place and route” reports in the subsequent sections.

3.1 The chip

Figure PR1 shows the chip and it’s connections. Figure PR2 shows the chip and the live “slices” and IOB (IO Blocks).

Figure PR1 shows the chip and it’s connections.

Figure PR2. All of the live IOB’s and “slices”

3.2 The Xilinx mapping report

Xilinx Mapping Report File for Design 'min8'

Copyright (c) 1995-2000 Xilinx, Inc. All rights reserved.

Design Information

------------------

Command Line : c:/xilinx_webpack/bin/nt/map.exe

C:/proj/min8/ls/min8_struct/netlists/min8

Target Device : x2v250

Target Package : fg456

Target Speed : -4

Mapper Version : virtex2 -- D.27

Mapped Date : Fri Jun 22 17:54:38 2001

Design Summary

--------------

Number of errors: 0

Number of warnings: 1

Number of Slices: 81 out of 1,536 5%

Number of Slices containing

unrelated logic: 0 out of 81 0%

Number of 4 input LUTs: 162 out of 3,072 5%

Number of bonded IOBs: 111 out of 200 55%

Total equivalent gate count for design: 1,269

Additional JTAG gate count for IOBs: 5,328

Table of Contents

-----------------

Section 1 - Errors

Section 2 - Warnings

Section 3 - Design Attributes

Section 4 - Removed Logic Summary

Section 5 - Removed Logic

Section 6 - Added Logic

Section 7 - Expanded Logic

Section 8 - Signal Cross-Reference

Section 9 - Symbol Cross-Reference

Section 10 - IOB Properties

Section 11 - RPMs

Section 12 - Guide Report

Section 13 - Area Group Summary

Section 14 - Modular Design Summary

Section 1 - Errors

------------------

Section 2 - Warnings

--------------------

WARNING:MapLib:62 - All of the external outputs in this design are using slew

rate limited output drivers. The delay on speed critical outputs can be

dramatically reduced by designating them as fast outputs in the schematic.

Section 3 - Design Attributes

-----------------------------

Section 4 - Removed Logic Summary

---------------------------------

1 block(s) optimized away

Section 5 - Removed Logic

-------------------------

Optimized Block(s):

TYPE BLOCK

GND I8_modgen_gt_0_nx2

To enable printing of redundant blocks removed and signals merged, set the

detailed map report option and rerun map.

Section 6 - Added Logic

-----------------------

Section 7 - Expanded Logic

--------------------------

To enable this section, set the detailed map report option and rerun map.

Section 8 - Signal Cross-Reference

----------------------------------

To enable this section, set the detailed map report option and rerun map.

Section 9 - Symbol Cross-Reference

----------------------------------

To enable this section, set the detailed map report option and rerun map.

Section 10 - IOB Properties

---------------------------

min_num(0) (IOB) : SLEW=SLOW DRIVE=12

min_num(1) (IOB) : SLEW=SLOW DRIVE=12

min_num(10) (IOB) : SLEW=SLOW DRIVE=12

min_num(11) (IOB) : SLEW=SLOW DRIVE=12

min_num(2) (IOB) : SLEW=SLOW DRIVE=12

min_num(3) (IOB) : SLEW=SLOW DRIVE=12

min_num(4) (IOB) : SLEW=SLOW DRIVE=12

min_num(5) (IOB) : SLEW=SLOW DRIVE=12

min_num(6) (IOB) : SLEW=SLOW DRIVE=12

min_num(7) (IOB) : SLEW=SLOW DRIVE=12

min_num(8) (IOB) : SLEW=SLOW DRIVE=12

min_num(9) (IOB) : SLEW=SLOW DRIVE=12

position(0) (IOB) : SLEW=SLOW DRIVE=12

position(1) (IOB) : SLEW=SLOW DRIVE=12

position(2) (IOB) : SLEW=SLOW DRIVE=12

sad_value0(0) (IOB)

sad_value0(1) (IOB)

sad_value0(10) (IOB)

sad_value0(11) (IOB)

sad_value0(2) (IOB)

sad_value0(3) (IOB)

sad_value0(4) (IOB)

sad_value0(5) (IOB)

sad_value0(6) (IOB)

sad_value0(7) (IOB)

sad_value0(8) (IOB)

sad_value0(9) (IOB)

sad_value1(0) (IOB)

sad_value1(1) (IOB)

sad_value1(10) (IOB)

sad_value1(11) (IOB)

sad_value1(2) (IOB)

sad_value1(3) (IOB)

sad_value1(4) (IOB)

sad_value1(5) (IOB)

sad_value1(6) (IOB)

sad_value1(7) (IOB)

sad_value1(8) (IOB)

sad_value1(9) (IOB)

sad_value2(0) (IOB)

sad_value2(1) (IOB)

sad_value2(10) (IOB)

sad_value2(11) (IOB)

sad_value2(2) (IOB)

sad_value2(3) (IOB)

sad_value2(4) (IOB)

sad_value2(5) (IOB)

sad_value2(6) (IOB)

sad_value2(7) (IOB)

sad_value2(8) (IOB)

sad_value2(9) (IOB)

sad_value3(0) (IOB)

sad_value3(1) (IOB)

sad_value3(10) (IOB)

sad_value3(11) (IOB)

sad_value3(2) (IOB)

sad_value3(3) (IOB)

sad_value3(4) (IOB)

sad_value3(5) (IOB)

sad_value3(6) (IOB)

sad_value3(7) (IOB)

sad_value3(8) (IOB)

sad_value3(9) (IOB)

sad_value4(0) (IOB)

sad_value4(1) (IOB)

sad_value4(10) (IOB)

sad_value4(11) (IOB)

sad_value4(2) (IOB)

sad_value4(3) (IOB)

sad_value4(4) (IOB)

sad_value4(5) (IOB)

sad_value4(6) (IOB)

sad_value4(7) (IOB)

sad_value4(8) (IOB)

sad_value4(9) (IOB)

sad_value5(0) (IOB)

sad_value5(1) (IOB)

sad_value5(10) (IOB)

sad_value5(11) (IOB)

sad_value5(2) (IOB)

sad_value5(3) (IOB)

sad_value5(4) (IOB)

sad_value5(5) (IOB)

sad_value5(6) (IOB)

sad_value5(7) (IOB)

sad_value5(8) (IOB)

sad_value5(9) (IOB)

sad_value6(0) (IOB)

sad_value6(1) (IOB)

sad_value6(10) (IOB)

sad_value6(11) (IOB)

sad_value6(2) (IOB)

sad_value6(3) (IOB)

sad_value6(4) (IOB)

sad_value6(5) (IOB)

sad_value6(6) (IOB)

sad_value6(7) (IOB)

sad_value6(8) (IOB)

sad_value6(9) (IOB)

sad_value7(0) (IOB)

sad_value7(1) (IOB)

sad_value7(10) (IOB)

sad_value7(11) (IOB)

sad_value7(2) (IOB)

sad_value7(3) (IOB)

sad_value7(4) (IOB)

sad_value7(5) (IOB)

sad_value7(6) (IOB)

sad_value7(7) (IOB)

sad_value7(8) (IOB)

sad_value7(9) (IOB)

Section 11 - RPMs

-----------------

Section 12 - Guide Report

-------------------------

Guide not run on this design.

Section 13 - Area Group Summary

-------------------------------

No area groups were found in this design.

Section 14 - Modular Design Summary

-----------------------------------

Modular Design not used for this design.

3.3 The Xilinx Place and route report

Release 3.3WP8.x - Par D.27

Fri Jun 22 17:54:45 2001

c:/xilinx_webpack/bin/nt/par.exe -d 1 -ol 2 -w

C:/proj/min8/ls/min8_struct/netlists/min8

C:/proj/min8/ls/min8_struct/netlists/min8_out.ncd

C:/proj/min8/ls/min8_struct/netlists/min8.pcf

Constraints file: C:/proj/min8/ls/min8_struct/netlists/min8.pcf

Loading design for application par from file

C:/proj/min8/ls/min8_struct/netlists/min8.ncd.

"min8" is an NCD, version 2.35, device xc2v250, package fg456, speed -4

Loading device for application par from file '2v250.nph' in environment

c:/xilinx_webpack.

Device speed data version: ADVANCED 1.80 2001-04-07.

Device utilization summary:

Number of External IOBs 111 out of 200 55%

Number of SLICEs 81 out of 1536 5%

Overall effort level (-ol): 2 (set by user)

Placer effort level (-pl): 2 (set by user)

Placer cost table entry (-t): 1

Router effort level (-rl): 2 (set by user)

Starting Clock Logic Placement. REAL time: 4 secs

Finished Clock Logic Placement. REAL time: 4 secs

Automatic resolution of clock placement was successful.

It was not necessary to constrain the placement of any of the logic driven by

the global clocks with the current clock placement.

######################################################

## Automatic clock placement completed.

######################################################

Starting Mincut Placer. REAL time: 5 secs

Finished Mincut Placer. REAL time: 5 secs

Dumping design to file C:/proj/min8/ls/min8_struct/netlists/min8_out.ncd.

Starting Directed Placer. REAL time: 5 secs

Placement pass 1 .

Placer score = 51920

Placer score = 51920

Starting Optimizing Placer. REAL time: 5 secs

Optimizing

Swapped 418 comps.

Xilinx Placer [1] 39280 REAL time: 5 secs

Finished Optimizing Placer. REAL time: 5 secs

Dumping design to file C:/proj/min8/ls/min8_struct/netlists/min8_out.ncd.

Total REAL time to Placer completion: 6 secs

Total CPU time to Placer completion: 4 secs

0 connection(s) routed; 551 unrouted active, 7 unrouted PWR/GND.

Starting router resource preassignment

Completed router resource preassignment. REAL time: 6 secs

Starting iterative routing.

Routing active signals.

........

End of iteration 1

558 successful; 0 unrouted; (0) REAL time: 8 secs

Constraints are met.

Dumping design to file C:/proj/min8/ls/min8_struct/netlists/min8_out.ncd.

Starting delay cleanup

Improving timing.

End of delay cleanup iteration 1

558 successful; 0 unrouted; (0) REAL time: 35 secs

Dumping design to file C:/proj/min8/ls/min8_struct/netlists/min8_out.ncd.

Total REAL time: 35 secs

Total CPU time: 32 secs

End of route. 558 routed (100.00%); 0 unrouted.

No errors found.

Completely routed.

This design was run without timing constraints. It is likely that much better

circuit performance can be obtained by trying either or both of the following:

- Enabling the Delay Based Cleanup router pass, if not already enabled

- Supplying timing constraints in the input design

Total REAL time to Router completion: 36 secs

Total CPU time to Router completion: 32 secs

Generating PAR statistics.

The Delay Summary Report

The Score for this design is: 158

The Number of signals not completely routed for this design is: 0

The Average Connection Delay for this design is: 1.150 ns

The Maximum Pin Delay is: 2.417 ns

The Average Connection Delay on the 10 Worst Nets is: 2.193 ns

Listing Pin Delays by value: (ns)

d < 1.00 < d < 2.00 < d < 3.00 < d < 4.00 < d < 5.00 d >= 5.00

--------- --------- --------- --------- --------- ---------

216 298 44 0 0 0

Dumping design to file C:/proj/min8/ls/min8_struct/netlists/min8_out.ncd.

All signals are completely routed.

Total REAL time to PAR completion: 37 secs

Total CPU time to PAR completion: 33 secs

Placement: Completed - No errors found.

Routing: Completed - No errors found.

PAR done.

3.4 Xilinx timing report

Xilinx TRACE, Version D.27

Copyright (c) 1995-2000 Xilinx, Inc. All rights reserved.

c:/xilinx_webpack/bin/nt/trce.exe C:/proj/min8/ls/min8_struct/netlists/min8_out

C:/proj/min8/ls/min8_struct/netlists/min8.pcf -v 3 -o

C:/proj/min8/ls/min8_struct/netlists/min8_out

Design file: min8_out.ncd

Physical constraint file: min8.pcf

Device,speed: xc2v250,-4 (ADVANCED 1.80 2001-04-07)

Report level: verbose report

--------------------------------------------------------------------------------

WARNING:Timing:2491 - No timing constraints found, doing default enumeration.

================================================================================

Timing constraint: Default period analysis

458304 items analyzed, 0 timing errors detected.

Maximum delay is 22.695ns.

--------------------------------------------------------------------------------

Delay: 22.695ns sad_value3(5) to min_num(7)

Path sad_value3(5) to min_num(7) contains 22 levels of logic:

Path starting from Comp: U13.PAD

To Delay type Delay(ns) Physical Resource

Logical Resource(s)

------------------------------------------------- --------

U13.I Tiopi 1.116R sad_value3(5)

sad_value3(5).PAD

sad_value3(5)_ibuf

SLICE_X11Y12.G1 net (fanout=2) 2.346R sad_value3(5)_int

SLICE_X11Y12.COUT Topcyg 0.592R I8_modgen_gt_0_ix51/O

I8_modgen_gt_0_ix49

I8_modgen_gt_0_ix51

SLICE_X11Y13.CIN net (fanout=1) 0.000R I8_modgen_gt_0_ix51/O

SLICE_X11Y13.COUT Tbyp 0.108R I8_modgen_gt_0_ix59/O

SLICE_X11Y14.CIN net (fanout=1) 0.000R I8_modgen_gt_0_ix59/O

SLICE_X11Y14.COUT Tbyp 0.108R I8_modgen_gt_0_ix67/O

SLICE_X11Y15.CIN net (fanout=1) 0.000R I8_modgen_gt_0_ix67/O

SLICE_X11Y15.COUT Tbyp 0.108R pos10(1)

SLICE_X7Y10.G3 net (fanout=15) 1.383R pos10(1)

SLICE_X7Y10.Y Tilo 0.445R lev20(1)

ix774

SLICE_X9Y10.G1 net (fanout=1) 0.570R lev10(1)

SLICE_X9Y10.COUT Topcyg 0.592R I12_modgen_gt_4_ix35/O

I12_modgen_gt_4_ix33

I12_modgen_gt_4_ix35

SLICE_X9Y11.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix35/O

SLICE_X9Y11.COUT Tbyp 0.108R I12_modgen_gt_4_ix43/O

SLICE_X9Y12.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix43/O

SLICE_X9Y12.COUT Tbyp 0.108R I12_modgen_gt_4_ix51/O

SLICE_X9Y13.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix51/O

SLICE_X9Y13.COUT Tbyp 0.108R I12_modgen_gt_4_ix59/O

SLICE_X9Y14.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix59/O

SLICE_X9Y14.COUT Tbyp 0.108R I12_modgen_gt_4_ix67/O

SLICE_X9Y15.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix67/O

SLICE_X9Y15.COUT Tbyp 0.108R I12_nx4

SLICE_X8Y11.BX net (fanout=15) 1.613R I12_nx4

SLICE_X8Y11.X Tbxx 0.689R lev20(0)

ix756

SLICE_X5Y12.F1 net (fanout=2) 0.835R lev20(0)

SLICE_X5Y12.COUT Topcyf 0.716R I14_modgen_gt_6_ix35/O

I14_modgen_gt_6_ix29

I14_modgen_gt_6_ix31

I14_modgen_gt_6_ix35

SLICE_X5Y13.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix35/O

SLICE_X5Y13.COUT Tbyp 0.108R I14_modgen_gt_6_ix43/O

SLICE_X5Y14.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix43/O

SLICE_X5Y14.COUT Tbyp 0.108R I14_modgen_gt_6_ix51/O

SLICE_X5Y15.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix51/O

SLICE_X5Y15.COUT Tbyp 0.108R I14_modgen_gt_6_ix59/O

SLICE_X5Y16.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix59/O

SLICE_X5Y16.COUT Tbyp 0.108R I14_modgen_gt_6_ix67/O

SLICE_X5Y17.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix67/O

SLICE_X5Y17.COUT Tbyp 0.108R I14_nx4

SLICE_X7Y14.G1 net (fanout=27) 1.132R I14_nx4

SLICE_X7Y14.Y Tilo 0.445R min_num_dup0(7)

ix817

SLICE_X7Y14.F3 net (fanout=1) 0.035R nx720

SLICE_X7Y14.X Tilo 0.445R min_num_dup0(7)

ix805

R21.O1 net (fanout=1) 2.034R min_num_dup0(7)

R21.PAD Tioop 6.303R min_num(7)

min_num(7)_obuf

min_num(7).PAD

-------------------------------------------------

Total (12.747ns logic, 9.948ns route) 22.695ns

(56.2% logic, 43.8% route)

--------------------------------------------------------------------------------

Delay: 22.689ns sad_value3(5) to min_num(7)

Path sad_value3(5) to min_num(7) contains 22 levels of logic:

Path starting from Comp: U13.PAD

To Delay type Delay(ns) Physical Resource

Logical Resource(s)

------------------------------------------------- --------

U13.I Tiopi 1.116R sad_value3(5)

sad_value3(5).PAD

sad_value3(5)_ibuf

SLICE_X11Y12.G1 net (fanout=2) 2.346R sad_value3(5)_int

SLICE_X11Y12.COUT Topcyg 0.592R I8_modgen_gt_0_ix51/O

I8_modgen_gt_0_ix49

I8_modgen_gt_0_ix51

SLICE_X11Y13.CIN net (fanout=1) 0.000R I8_modgen_gt_0_ix51/O

SLICE_X11Y13.COUT Tbyp 0.108R I8_modgen_gt_0_ix59/O

SLICE_X11Y14.CIN net (fanout=1) 0.000R I8_modgen_gt_0_ix59/O

SLICE_X11Y14.COUT Tbyp 0.108R I8_modgen_gt_0_ix67/O

SLICE_X11Y15.CIN net (fanout=1) 0.000R I8_modgen_gt_0_ix67/O

SLICE_X11Y15.COUT Tbyp 0.108R pos10(1)

SLICE_X8Y11.G2 net (fanout=15) 1.290R pos10(1)

SLICE_X8Y11.Y Tilo 0.445R lev20(0)

ix775

SLICE_X9Y10.F1 net (fanout=1) 0.533R lev10(0)

SLICE_X9Y10.COUT Topcyf 0.716R I12_modgen_gt_4_ix35/O

I12_modgen_gt_4_ix29

I12_modgen_gt_4_ix31

I12_modgen_gt_4_ix35

SLICE_X9Y11.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix35/O

SLICE_X9Y11.COUT Tbyp 0.108R I12_modgen_gt_4_ix43/O

SLICE_X9Y12.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix43/O

SLICE_X9Y12.COUT Tbyp 0.108R I12_modgen_gt_4_ix51/O

SLICE_X9Y13.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix51/O

SLICE_X9Y13.COUT Tbyp 0.108R I12_modgen_gt_4_ix59/O

SLICE_X9Y14.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix59/O

SLICE_X9Y14.COUT Tbyp 0.108R I12_modgen_gt_4_ix67/O

SLICE_X9Y15.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix67/O

SLICE_X9Y15.COUT Tbyp 0.108R I12_nx4

SLICE_X8Y11.BX net (fanout=15) 1.613R I12_nx4

SLICE_X8Y11.X Tbxx 0.689R lev20(0)

ix756

SLICE_X5Y12.F1 net (fanout=2) 0.835R lev20(0)

SLICE_X5Y12.COUT Topcyf 0.716R I14_modgen_gt_6_ix35/O

I14_modgen_gt_6_ix29

I14_modgen_gt_6_ix31

I14_modgen_gt_6_ix35

SLICE_X5Y13.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix35/O

SLICE_X5Y13.COUT Tbyp 0.108R I14_modgen_gt_6_ix43/O

SLICE_X5Y14.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix43/O

SLICE_X5Y14.COUT Tbyp 0.108R I14_modgen_gt_6_ix51/O

SLICE_X5Y15.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix51/O

SLICE_X5Y15.COUT Tbyp 0.108R I14_modgen_gt_6_ix59/O

SLICE_X5Y16.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix59/O

SLICE_X5Y16.COUT Tbyp 0.108R I14_modgen_gt_6_ix67/O

SLICE_X5Y17.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix67/O

SLICE_X5Y17.COUT Tbyp 0.108R I14_nx4

SLICE_X7Y14.G1 net (fanout=27) 1.132R I14_nx4

SLICE_X7Y14.Y Tilo 0.445R min_num_dup0(7)

ix817

SLICE_X7Y14.F3 net (fanout=1) 0.035R nx720

SLICE_X7Y14.X Tilo 0.445R min_num_dup0(7)

ix805

R21.O1 net (fanout=1) 2.034R min_num_dup0(7)

R21.PAD Tioop 6.303R min_num(7)

min_num(7)_obuf

min_num(7).PAD

-------------------------------------------------

Total (12.871ns logic, 9.818ns route) 22.689ns

(56.7% logic, 43.3% route)

--------------------------------------------------------------------------------

Delay: 22.666ns sad_value3(5) to min_num(4)

Path sad_value3(5) to min_num(4) contains 22 levels of logic:

Path starting from Comp: U13.PAD

To Delay type Delay(ns) Physical Resource

Logical Resource(s)

------------------------------------------------- --------

U13.I Tiopi 1.116R sad_value3(5)

sad_value3(5).PAD

sad_value3(5)_ibuf

SLICE_X11Y12.G1 net (fanout=2) 2.346R sad_value3(5)_int

SLICE_X11Y12.COUT Topcyg 0.592R I8_modgen_gt_0_ix51/O

I8_modgen_gt_0_ix49

I8_modgen_gt_0_ix51

SLICE_X11Y13.CIN net (fanout=1) 0.000R I8_modgen_gt_0_ix51/O

SLICE_X11Y13.COUT Tbyp 0.108R I8_modgen_gt_0_ix59/O

SLICE_X11Y14.CIN net (fanout=1) 0.000R I8_modgen_gt_0_ix59/O

SLICE_X11Y14.COUT Tbyp 0.108R I8_modgen_gt_0_ix67/O

SLICE_X11Y15.CIN net (fanout=1) 0.000R I8_modgen_gt_0_ix67/O

SLICE_X11Y15.COUT Tbyp 0.108R pos10(1)

SLICE_X7Y10.G3 net (fanout=15) 1.383R pos10(1)

SLICE_X7Y10.Y Tilo 0.445R lev20(1)

ix774

SLICE_X9Y10.G1 net (fanout=1) 0.570R lev10(1)

SLICE_X9Y10.COUT Topcyg 0.592R I12_modgen_gt_4_ix35/O

I12_modgen_gt_4_ix33

I12_modgen_gt_4_ix35

SLICE_X9Y11.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix35/O

SLICE_X9Y11.COUT Tbyp 0.108R I12_modgen_gt_4_ix43/O

SLICE_X9Y12.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix43/O

SLICE_X9Y12.COUT Tbyp 0.108R I12_modgen_gt_4_ix51/O

SLICE_X9Y13.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix51/O

SLICE_X9Y13.COUT Tbyp 0.108R I12_modgen_gt_4_ix59/O

SLICE_X9Y14.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix59/O

SLICE_X9Y14.COUT Tbyp 0.108R I12_modgen_gt_4_ix67/O

SLICE_X9Y15.CIN net (fanout=1) 0.000R I12_modgen_gt_4_ix67/O

SLICE_X9Y15.COUT Tbyp 0.108R I12_nx4

SLICE_X8Y11.BX net (fanout=15) 1.613R I12_nx4

SLICE_X8Y11.X Tbxx 0.689R lev20(0)

ix756

SLICE_X5Y12.F1 net (fanout=2) 0.835R lev20(0)

SLICE_X5Y12.COUT Topcyf 0.716R I14_modgen_gt_6_ix35/O

I14_modgen_gt_6_ix29

I14_modgen_gt_6_ix31

I14_modgen_gt_6_ix35

SLICE_X5Y13.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix35/O

SLICE_X5Y13.COUT Tbyp 0.108R I14_modgen_gt_6_ix43/O

SLICE_X5Y14.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix43/O

SLICE_X5Y14.COUT Tbyp 0.108R I14_modgen_gt_6_ix51/O

SLICE_X5Y15.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix51/O

SLICE_X5Y15.COUT Tbyp 0.108R I14_modgen_gt_6_ix59/O

SLICE_X5Y16.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix59/O

SLICE_X5Y16.COUT Tbyp 0.108R I14_modgen_gt_6_ix67/O

SLICE_X5Y17.CIN net (fanout=1) 0.000R I14_modgen_gt_6_ix67/O

SLICE_X5Y17.COUT Tbyp 0.108R I14_nx4

SLICE_X0Y14.G2 net (fanout=27) 1.619R I14_nx4

SLICE_X0Y14.Y Tilo 0.445R min_num_dup0(4)

ix820

SLICE_X0Y14.F4 net (fanout=1) 0.002R nx723

SLICE_X0Y14.X Tilo 0.445R min_num_dup0(4)

ix808

E4.O1 net (fanout=1) 1.551R min_num_dup0(4)

E4.PAD Tioop 6.303R min_num(4)

min_num(4)_obuf

min_num(4).PAD

-------------------------------------------------

Total (12.747ns logic, 9.919ns route) 22.666ns

(56.2% logic, 43.8% route)

--------------------------------------------------------------------------------

================================================================================

Timing constraint: Default net enumeration

216 items analyzed, 0 timing errors detected.

Maximum net delay is 2.417ns.

--------------------------------------------------------------------------------

Delay: 2.417ns sad_value2(0)_int

From To Delay(ns)

AA18.I SLICE_X8Y11.F2 2.417

AA18.I SLICE_X13Y10.F1 2.216

AA18.I SLICE_X9Y10.F4 2.065

--------------------------------------------------------------------------------

Delay: 2.359ns sad_value2(9)_int

From To Delay(ns)

M21.I SLICE_X8Y15.F1 2.359

M21.I SLICE_X13Y14.G1 1.850

M21.I SLICE_X9Y14.G3 2.114

--------------------------------------------------------------------------------

Delay: 2.346ns sad_value3(5)_int

From To Delay(ns)

U13.I SLICE_X10Y13.G2 1.994

U13.I SLICE_X11Y12.G1 2.346

--------------------------------------------------------------------------------

All constraints were met.

Data Sheet report:

-----------------

All values displayed in nanoseconds (ns)

Pad to Pad

---------------+---------------+---------+

Source Pad |Destination Pad| Delay |

---------------+---------------+---------+

sad_value0(0) |min_num(0) | 18.688|

sad_value0(0) |min_num(1) | 18.173|

sad_value0(0) |min_num(10) | 18.336|

sad_value0(0) |min_num(11) | 18.979|

sad_value0(0) |min_num(2) | 18.305|

sad_value0(0) |min_num(3) | 18.157|

sad_value0(0) |min_num(4) | 19.267|

sad_value0(0) |min_num(5) | 19.212|

sad_value0(0) |min_num(6) | 18.996|

sad_value0(0) |min_num(7) | 19.296|

sad_value0(0) |min_num(8) | 19.076|

sad_value0(0) |min_num(9) | 18.945|

sad_value0(0) |position(0) | 18.030|

sad_value0(0) |position(1) | 18.684|

sad_value0(0) |position(2) | 17.835|

sad_value0(1) |min_num(0) | 18.382|

sad_value0(1) |min_num(1) | 17.867|

sad_value0(1) |min_num(10) | 18.030|

sad_value0(1) |min_num(11) | 18.673|

sad_value0(1) |min_num(2) | 17.999|

sad_value0(1) |min_num(3) | 17.851|

sad_value0(1) |min_num(4) | 18.961|

sad_value0(1) |min_num(5) | 18.906|

sad_value0(1) |min_num(6) | 18.690|

sad_value0(1) |min_num(7) | 18.990|

sad_value0(1) |min_num(8) | 18.770|

sad_value0(1) |min_num(9) | 18.639|

sad_value0(1) |position(0) | 17.724|

sad_value0(1) |position(1) | 18.378|

sad_value0(1) |position(2) | 17.529|

sad_value0(10) |min_num(0) | 18.449|

sad_value0(10) |min_num(1) | 17.934|

sad_value0(10) |min_num(10) | 18.097|

sad_value0(10) |min_num(11) | 18.740|

sad_value0(10) |min_num(2) | 18.066|

sad_value0(10) |min_num(3) | 17.918|

sad_value0(10) |min_num(4) | 19.028|

sad_value0(10) |min_num(5) | 18.973|

sad_value0(10) |min_num(6) | 18.757|

sad_value0(10) |min_num(7) | 19.057|

sad_value0(10) |min_num(8) | 18.837|

sad_value0(10) |min_num(9) | 18.706|

sad_value0(10) |position(0) | 17.791|

sad_value0(10) |position(1) | 18.445|

sad_value0(10) |position(2) | 17.596|

sad_value0(11) |min_num(0) | 17.336|

sad_value0(11) |min_num(1) | 16.821|

sad_value0(11) |min_num(10) | 16.984|

sad_value0(11) |min_num(11) | 17.627|

sad_value0(11) |min_num(2) | 16.953|

sad_value0(11) |min_num(3) | 16.805|

sad_value0(11) |min_num(4) | 17.915|

sad_value0(11) |min_num(5) | 17.860|

sad_value0(11) |min_num(6) | 17.644|

sad_value0(11) |min_num(7) | 17.944|

sad_value0(11) |min_num(8) | 17.724|

sad_value0(11) |min_num(9) | 17.593|

sad_value0(11) |position(0) | 16.678|

sad_value0(11) |position(1) | 17.332|

sad_value0(11) |position(2) | 16.483|

sad_value0(2) |min_num(0) | 17.905|

sad_value0(2) |min_num(1) | 17.390|

sad_value0(2) |min_num(10) | 17.553|

sad_value0(2) |min_num(11) | 18.196|

sad_value0(2) |min_num(2) | 17.522|

sad_value0(2) |min_num(3) | 17.374|

sad_value0(2) |min_num(4) | 18.484|

sad_value0(2) |min_num(5) | 18.429|

sad_value0(2) |min_num(6) | 18.213|

sad_value0(2) |min_num(7) | 18.513|

sad_value0(2) |min_num(8) | 18.293|

sad_value0(2) |min_num(9) | 18.162|

sad_value0(2) |position(0) | 17.247|

sad_value0(2) |position(1) | 17.901|

sad_value0(2) |position(2) | 17.052|

sad_value0(3) |min_num(0) | 17.996|

sad_value0(3) |min_num(1) | 17.481|

sad_value0(3) |min_num(10) | 17.644|

sad_value0(3) |min_num(11) | 18.287|

sad_value0(3) |min_num(2) | 17.613|

sad_value0(3) |min_num(3) | 17.465|

sad_value0(3) |min_num(4) | 18.575|

sad_value0(3) |min_num(5) | 18.520|

sad_value0(3) |min_num(6) | 18.304|

sad_value0(3) |min_num(7) | 18.604|

sad_value0(3) |min_num(8) | 18.384|

sad_value0(3) |min_num(9) | 18.253|

sad_value0(3) |position(0) | 17.338|

sad_value0(3) |position(1) | 17.992|

sad_value0(3) |position(2) | 17.143|

sad_value0(4) |min_num(0) | 18.371|

sad_value0(4) |min_num(1) | 17.856|

sad_value0(4) |min_num(10) | 18.019|

sad_value0(4) |min_num(11) | 18.662|

sad_value0(4) |min_num(2) | 17.988|

sad_value0(4) |min_num(3) | 17.840|

sad_value0(4) |min_num(4) | 18.950|

sad_value0(4) |min_num(5) | 18.895|

sad_value0(4) |min_num(6) | 18.679|

sad_value0(4) |min_num(7) | 18.979|

sad_value0(4) |min_num(8) | 18.759|

sad_value0(4) |min_num(9) | 18.628|

sad_value0(4) |position(0) | 17.713|

sad_value0(4) |position(1) | 18.367|

sad_value0(4) |position(2) | 17.518|

sad_value0(5) |min_num(0) | 18.620|

sad_value0(5) |min_num(1) | 18.105|

sad_value0(5) |min_num(10) | 18.268|

sad_value0(5) |min_num(11) | 18.911|

sad_value0(5) |min_num(2) | 18.237|

sad_value0(5) |min_num(3) | 18.089|

sad_value0(5) |min_num(4) | 19.199|

sad_value0(5) |min_num(5) | 19.144|

sad_value0(5) |min_num(6) | 18.928|

sad_value0(5) |min_num(7) | 19.228|

sad_value0(5) |min_num(8) | 19.008|

sad_value0(5) |min_num(9) | 18.877|

sad_value0(5) |position(0) | 17.962|

sad_value0(5) |position(1) | 18.616|

sad_value0(5) |position(2) | 17.767|

sad_value0(6) |min_num(0) | 18.511|

sad_value0(6) |min_num(1) | 17.996|

sad_value0(6) |min_num(10) | 18.159|

sad_value0(6) |min_num(11) | 18.802|

sad_value0(6) |min_num(2) | 18.128|

sad_value0(6) |min_num(3) | 17.980|

sad_value0(6) |min_num(4) | 19.090|

sad_value0(6) |min_num(5) | 19.035|

sad_value0(6) |min_num(6) | 18.819|

sad_value0(6) |min_num(7) | 19.119|

sad_value0(6) |min_num(8) | 18.899|

sad_value0(6) |min_num(9) | 18.768|

sad_value0(6) |position(0) | 17.853|

sad_value0(6) |position(1) | 18.507|

sad_value0(6) |position(2) | 17.658|

sad_value0(7) |min_num(0) | 18.512|

sad_value0(7) |min_num(1) | 17.997|

sad_value0(7) |min_num(10) | 18.160|

sad_value0(7) |min_num(11) | 18.803|

sad_value0(7) |min_num(2) | 18.129|

sad_value0(7) |min_num(3) | 17.981|

sad_value0(7) |min_num(4) | 19.091|

sad_value0(7) |min_num(5) | 19.036|

sad_value0(7) |min_num(6) | 18.820|

sad_value0(7) |min_num(7) | 19.120|

sad_value0(7) |min_num(8) | 18.900|

sad_value0(7) |min_num(9) | 18.769|

sad_value0(7) |position(0) | 17.854|

sad_value0(7) |position(1) | 18.508|

sad_value0(7) |position(2) | 17.659|

sad_value0(8) |min_num(0) | 17.597|

sad_value0(8) |min_num(1) | 17.082|

sad_value0(8) |min_num(10) | 17.245|

sad_value0(8) |min_num(11) | 17.888|

sad_value0(8) |min_num(2) | 17.214|

sad_value0(8) |min_num(3) | 17.066|

sad_value0(8) |min_num(4) | 18.176|

sad_value0(8) |min_num(5) | 18.121|

sad_value0(8) |min_num(6) | 17.905|

sad_value0(8) |min_num(7) | 18.205|

sad_value0(8) |min_num(8) | 17.985|

sad_value0(8) |min_num(9) | 17.854|

sad_value0(8) |position(0) | 16.939|

sad_value0(8) |position(1) | 17.593|

sad_value0(8) |position(2) | 16.744|

sad_value0(9) |min_num(0) | 18.447|

sad_value0(9) |min_num(1) | 17.932|

sad_value0(9) |min_num(10) | 18.095|

sad_value0(9) |min_num(11) | 18.738|

sad_value0(9) |min_num(2) | 18.064|

sad_value0(9) |min_num(3) | 17.916|

sad_value0(9) |min_num(4) | 19.026|

sad_value0(9) |min_num(5) | 18.971|

sad_value0(9) |min_num(6) | 18.755|

sad_value0(9) |min_num(7) | 19.055|

sad_value0(9) |min_num(8) | 18.835|

sad_value0(9) |min_num(9) | 18.704|

sad_value0(9) |position(0) | 17.789|

sad_value0(9) |position(1) | 18.443|

sad_value0(9) |position(2) | 17.594|

sad_value1(0) |min_num(0) | 19.897|

sad_value1(0) |min_num(1) | 19.382|

sad_value1(0) |min_num(10) | 19.545|

sad_value1(0) |min_num(11) | 20.188|

sad_value1(0) |min_num(2) | 19.514|

sad_value1(0) |min_num(3) | 19.366|

sad_value1(0) |min_num(4) | 20.476|

sad_value1(0) |min_num(5) | 20.421|

sad_value1(0) |min_num(6) | 20.205|

sad_value1(0) |min_num(7) | 20.505|

sad_value1(0) |min_num(8) | 20.285|

sad_value1(0) |min_num(9) | 20.154|

sad_value1(0) |position(0) | 19.239|

sad_value1(0) |position(1) | 19.893|

sad_value1(0) |position(2) | 19.044|

sad_value1(1) |min_num(0) | 19.652|

sad_value1(1) |min_num(1) | 19.137|

sad_value1(1) |min_num(10) | 19.300|

sad_value1(1) |min_num(11) | 19.943|

sad_value1(1) |min_num(2) | 19.269|

sad_value1(1) |min_num(3) | 19.121|

sad_value1(1) |min_num(4) | 20.231|

sad_value1(1) |min_num(5) | 20.176|

sad_value1(1) |min_num(6) | 19.960|

sad_value1(1) |min_num(7) | 20.260|

sad_value1(1) |min_num(8) | 20.040|

sad_value1(1) |min_num(9) | 19.909|

sad_value1(1) |position(0) | 18.994|

sad_value1(1) |position(1) | 19.648|

sad_value1(1) |position(2) | 18.799|

sad_value1(10) |min_num(0) | 19.676|

sad_value1(10) |min_num(1) | 19.161|

sad_value1(10) |min_num(10) | 19.324|

sad_value1(10) |min_num(11) | 19.967|

sad_value1(10) |min_num(2) | 19.293|

sad_value1(10) |min_num(3) | 19.145|

sad_value1(10) |min_num(4) | 20.255|

sad_value1(10) |min_num(5) | 20.200|

sad_value1(10) |min_num(6) | 19.984|

sad_value1(10) |min_num(7) | 20.284|

sad_value1(10) |min_num(8) | 20.064|

sad_value1(10) |min_num(9) | 19.933|

sad_value1(10) |position(0) | 19.018|

sad_value1(10) |position(1) | 19.672|

sad_value1(10) |position(2) | 18.823|

sad_value1(11) |min_num(0) | 19.314|

sad_value1(11) |min_num(1) | 18.799|

sad_value1(11) |min_num(10) | 18.962|

sad_value1(11) |min_num(11) | 19.605|

sad_value1(11) |min_num(2) | 18.931|

sad_value1(11) |min_num(3) | 18.783|

sad_value1(11) |min_num(4) | 19.893|

sad_value1(11) |min_num(5) | 19.838|

sad_value1(11) |min_num(6) | 19.622|

sad_value1(11) |min_num(7) | 19.922|

sad_value1(11) |min_num(8) | 19.702|

sad_value1(11) |min_num(9) | 19.571|

sad_value1(11) |position(0) | 18.656|

sad_value1(11) |position(1) | 19.310|

sad_value1(11) |position(2) | 18.461|

sad_value1(2) |min_num(0) | 19.416|

sad_value1(2) |min_num(1) | 18.901|

sad_value1(2) |min_num(10) | 19.064|

sad_value1(2) |min_num(11) | 19.707|

sad_value1(2) |min_num(2) | 19.033|

sad_value1(2) |min_num(3) | 18.885|

sad_value1(2) |min_num(4) | 19.995|

sad_value1(2) |min_num(5) | 19.940|

sad_value1(2) |min_num(6) | 19.724|

sad_value1(2) |min_num(7) | 20.024|

sad_value1(2) |min_num(8) | 19.804|

sad_value1(2) |min_num(9) | 19.673|

sad_value1(2) |position(0) | 18.758|

sad_value1(2) |position(1) | 19.412|

sad_value1(2) |position(2) | 18.563|

sad_value1(3) |min_num(0) | 19.515|

sad_value1(3) |min_num(1) | 19.000|

sad_value1(3) |min_num(10) | 19.163|

sad_value1(3) |min_num(11) | 19.806|

sad_value1(3) |min_num(2) | 19.132|

sad_value1(3) |min_num(3) | 18.984|

sad_value1(3) |min_num(4) | 20.094|

sad_value1(3) |min_num(5) | 20.039|

sad_value1(3) |min_num(6) | 19.823|

sad_value1(3) |min_num(7) | 20.123|

sad_value1(3) |min_num(8) | 19.903|

sad_value1(3) |min_num(9) | 19.772|

sad_value1(3) |position(0) | 18.857|

sad_value1(3) |position(1) | 19.511|

sad_value1(3) |position(2) | 18.662|

sad_value1(4) |min_num(0) | 19.739|

sad_value1(4) |min_num(1) | 19.224|

sad_value1(4) |min_num(10) | 19.387|

sad_value1(4) |min_num(11) | 20.030|

sad_value1(4) |min_num(2) | 19.356|

sad_value1(4) |min_num(3) | 19.208|

sad_value1(4) |min_num(4) | 20.318|

sad_value1(4) |min_num(5) | 20.263|

sad_value1(4) |min_num(6) | 20.047|

sad_value1(4) |min_num(7) | 20.347|

sad_value1(4) |min_num(8) | 20.127|

sad_value1(4) |min_num(9) | 19.996|

sad_value1(4) |position(0) | 19.081|

sad_value1(4) |position(1) | 19.735|

sad_value1(4) |position(2) | 18.886|

sad_value1(5) |min_num(0) | 19.392|

sad_value1(5) |min_num(1) | 18.877|

sad_value1(5) |min_num(10) | 19.040|

sad_value1(5) |min_num(11) | 19.683|

sad_value1(5) |min_num(2) | 19.009|

sad_value1(5) |min_num(3) | 18.861|

sad_value1(5) |min_num(4) | 19.971|

sad_value1(5) |min_num(5) | 19.916|

sad_value1(5) |min_num(6) | 19.700|

sad_value1(5) |min_num(7) | 20.000|

sad_value1(5) |min_num(8) | 19.780|

sad_value1(5) |min_num(9) | 19.649|

sad_value1(5) |position(0) | 18.734|

sad_value1(5) |position(1) | 19.388|

sad_value1(5) |position(2) | 18.539|

sad_value1(6) |min_num(0) | 20.001|

sad_value1(6) |min_num(1) | 19.486|

sad_value1(6) |min_num(10) | 19.649|

sad_value1(6) |min_num(11) | 20.292|

sad_value1(6) |min_num(2) | 19.618|

sad_value1(6) |min_num(3) | 19.470|

sad_value1(6) |min_num(4) | 20.580|

sad_value1(6) |min_num(5) | 20.525|

sad_value1(6) |min_num(6) | 20.309|

sad_value1(6) |min_num(7) | 20.609|

sad_value1(6) |min_num(8) | 20.389|

sad_value1(6) |min_num(9) | 20.258|

sad_value1(6) |position(0) | 19.343|

sad_value1(6) |position(1) | 19.997|

sad_value1(6) |position(2) | 19.148|

sad_value1(7) |min_num(0) | 18.823|

sad_value1(7) |min_num(1) | 18.308|

sad_value1(7) |min_num(10) | 18.471|

sad_value1(7) |min_num(11) | 19.114|

sad_value1(7) |min_num(2) | 18.440|

sad_value1(7) |min_num(3) | 18.292|

sad_value1(7) |min_num(4) | 19.402|

sad_value1(7) |min_num(5) | 19.347|

sad_value1(7) |min_num(6) | 19.131|

sad_value1(7) |min_num(7) | 19.431|

sad_value1(7) |min_num(8) | 19.211|

sad_value1(7) |min_num(9) | 19.080|

sad_value1(7) |position(0) | 18.165|

sad_value1(7) |position(1) | 18.819|

sad_value1(7) |position(2) | 17.970|

sad_value1(8) |min_num(0) | 19.376|

sad_value1(8) |min_num(1) | 18.861|

sad_value1(8) |min_num(10) | 19.024|

sad_value1(8) |min_num(11) | 19.667|

sad_value1(8) |min_num(2) | 18.993|

sad_value1(8) |min_num(3) | 18.845|

sad_value1(8) |min_num(4) | 19.955|

sad_value1(8) |min_num(5) | 19.900|

sad_value1(8) |min_num(6) | 19.684|

sad_value1(8) |min_num(7) | 19.984|

sad_value1(8) |min_num(8) | 19.764|

sad_value1(8) |min_num(9) | 19.633|

sad_value1(8) |position(0) | 18.718|

sad_value1(8) |position(1) | 19.372|

sad_value1(8) |position(2) | 18.523|

sad_value1(9) |min_num(0) | 19.475|

sad_value1(9) |min_num(1) | 18.960|

sad_value1(9) |min_num(10) | 19.123|

sad_value1(9) |min_num(11) | 19.766|

sad_value1(9) |min_num(2) | 19.092|

sad_value1(9) |min_num(3) | 18.944|

sad_value1(9) |min_num(4) | 20.054|

sad_value1(9) |min_num(5) | 19.999|

sad_value1(9) |min_num(6) | 19.783|

sad_value1(9) |min_num(7) | 20.083|

sad_value1(9) |min_num(8) | 19.863|

sad_value1(9) |min_num(9) | 19.732|

sad_value1(9) |position(0) | 18.817|

sad_value1(9) |position(1) | 19.471|

sad_value1(9) |position(2) | 18.622|

sad_value2(0) |min_num(0) | 21.350|

sad_value2(0) |min_num(1) | 20.835|

sad_value2(0) |min_num(10) | 20.998|

sad_value2(0) |min_num(11) | 21.641|

sad_value2(0) |min_num(2) | 20.967|

sad_value2(0) |min_num(3) | 20.819|

sad_value2(0) |min_num(4) | 21.929|

sad_value2(0) |min_num(5) | 21.874|

sad_value2(0) |min_num(6) | 21.658|

sad_value2(0) |min_num(7) | 21.958|

sad_value2(0) |min_num(8) | 21.738|

sad_value2(0) |min_num(9) | 21.607|

sad_value2(0) |position(0) | 20.692|

sad_value2(0) |position(1) | 21.346|

sad_value2(0) |position(2) | 20.497|

sad_value2(1) |min_num(0) | 20.488|

sad_value2(1) |min_num(1) | 19.973|

sad_value2(1) |min_num(10) | 20.136|

sad_value2(1) |min_num(11) | 20.779|

sad_value2(1) |min_num(2) | 20.105|

sad_value2(1) |min_num(3) | 19.957|

sad_value2(1) |min_num(4) | 21.067|

sad_value2(1) |min_num(5) | 21.012|

sad_value2(1) |min_num(6) | 20.796|

sad_value2(1) |min_num(7) | 21.096|

sad_value2(1) |min_num(8) | 20.876|

sad_value2(1) |min_num(9) | 20.745|

sad_value2(1) |position(0) | 19.830|

sad_value2(1) |position(1) | 20.484|

sad_value2(1) |position(2) | 19.635|

sad_value2(10) |min_num(0) | 20.496|

sad_value2(10) |min_num(1) | 19.981|

sad_value2(10) |min_num(10) | 20.144|

sad_value2(10) |min_num(11) | 20.787|

sad_value2(10) |min_num(2) | 20.113|

sad_value2(10) |min_num(3) | 19.965|

sad_value2(10) |min_num(4) | 21.075|

sad_value2(10) |min_num(5) | 21.020|

sad_value2(10) |min_num(6) | 20.804|

sad_value2(10) |min_num(7) | 21.104|

sad_value2(10) |min_num(8) | 20.884|

sad_value2(10) |min_num(9) | 20.753|

sad_value2(10) |position(0) | 19.838|

sad_value2(10) |position(1) | 20.492|

sad_value2(10) |position(2) | 19.643|

sad_value2(11) |min_num(0) | 19.992|

sad_value2(11) |min_num(1) | 19.477|

sad_value2(11) |min_num(10) | 19.640|

sad_value2(11) |min_num(11) | 20.283|

sad_value2(11) |min_num(2) | 19.609|

sad_value2(11) |min_num(3) | 19.461|

sad_value2(11) |min_num(4) | 20.571|

sad_value2(11) |min_num(5) | 20.516|

sad_value2(11) |min_num(6) | 20.300|

sad_value2(11) |min_num(7) | 20.600|

sad_value2(11) |min_num(8) | 20.380|

sad_value2(11) |min_num(9) | 20.249|

sad_value2(11) |position(0) | 19.334|

sad_value2(11) |position(1) | 19.988|

sad_value2(11) |position(2) | 19.139|

sad_value2(2) |min_num(0) | 20.473|

sad_value2(2) |min_num(1) | 19.958|

sad_value2(2) |min_num(10) | 20.121|

sad_value2(2) |min_num(11) | 20.764|

sad_value2(2) |min_num(2) | 20.090|

sad_value2(2) |min_num(3) | 19.942|

sad_value2(2) |min_num(4) | 21.052|

sad_value2(2) |min_num(5) | 20.997|

sad_value2(2) |min_num(6) | 20.781|

sad_value2(2) |min_num(7) | 21.081|

sad_value2(2) |min_num(8) | 20.861|

sad_value2(2) |min_num(9) | 20.730|

sad_value2(2) |position(0) | 19.815|

sad_value2(2) |position(1) | 20.469|

sad_value2(2) |position(2) | 19.620|

sad_value2(3) |min_num(0) | 20.815|

sad_value2(3) |min_num(1) | 20.300|

sad_value2(3) |min_num(10) | 20.463|

sad_value2(3) |min_num(11) | 21.106|

sad_value2(3) |min_num(2) | 20.432|

sad_value2(3) |min_num(3) | 20.284|

sad_value2(3) |min_num(4) | 21.394|

sad_value2(3) |min_num(5) | 21.339|

sad_value2(3) |min_num(6) | 21.123|

sad_value2(3) |min_num(7) | 21.423|

sad_value2(3) |min_num(8) | 21.203|

sad_value2(3) |min_num(9) | 21.072|

sad_value2(3) |position(0) | 20.157|

sad_value2(3) |position(1) | 20.811|

sad_value2(3) |position(2) | 19.962|

sad_value2(4) |min_num(0) | 20.340|

sad_value2(4) |min_num(1) | 19.825|

sad_value2(4) |min_num(10) | 19.988|

sad_value2(4) |min_num(11) | 20.631|

sad_value2(4) |min_num(2) | 19.957|

sad_value2(4) |min_num(3) | 19.809|

sad_value2(4) |min_num(4) | 20.919|

sad_value2(4) |min_num(5) | 20.864|

sad_value2(4) |min_num(6) | 20.648|

sad_value2(4) |min_num(7) | 20.948|

sad_value2(4) |min_num(8) | 20.728|

sad_value2(4) |min_num(9) | 20.597|

sad_value2(4) |position(0) | 19.682|

sad_value2(4) |position(1) | 20.336|

sad_value2(4) |position(2) | 19.487|

sad_value2(5) |min_num(0) | 20.651|

sad_value2(5) |min_num(1) | 20.136|

sad_value2(5) |min_num(10) | 20.299|

sad_value2(5) |min_num(11) | 20.942|

sad_value2(5) |min_num(2) | 20.268|

sad_value2(5) |min_num(3) | 20.120|

sad_value2(5) |min_num(4) | 21.230|

sad_value2(5) |min_num(5) | 21.175|

sad_value2(5) |min_num(6) | 20.959|

sad_value2(5) |min_num(7) | 21.259|

sad_value2(5) |min_num(8) | 21.039|

sad_value2(5) |min_num(9) | 20.908|

sad_value2(5) |position(0) | 19.993|

sad_value2(5) |position(1) | 20.647|

sad_value2(5) |position(2) | 19.798|

sad_value2(6) |min_num(0) | 20.627|

sad_value2(6) |min_num(1) | 20.112|

sad_value2(6) |min_num(10) | 20.275|

sad_value2(6) |min_num(11) | 20.918|

sad_value2(6) |min_num(2) | 20.244|

sad_value2(6) |min_num(3) | 20.096|

sad_value2(6) |min_num(4) | 21.206|

sad_value2(6) |min_num(5) | 21.151|

sad_value2(6) |min_num(6) | 20.935|

sad_value2(6) |min_num(7) | 21.235|

sad_value2(6) |min_num(8) | 21.015|

sad_value2(6) |min_num(9) | 20.884|

sad_value2(6) |position(0) | 19.969|

sad_value2(6) |position(1) | 20.623|

sad_value2(6) |position(2) | 19.774|

sad_value2(7) |min_num(0) | 20.180|

sad_value2(7) |min_num(1) | 19.665|

sad_value2(7) |min_num(10) | 19.828|

sad_value2(7) |min_num(11) | 20.471|

sad_value2(7) |min_num(2) | 19.797|

sad_value2(7) |min_num(3) | 19.649|

sad_value2(7) |min_num(4) | 20.759|

sad_value2(7) |min_num(5) | 20.704|

sad_value2(7) |min_num(6) | 20.488|

sad_value2(7) |min_num(7) | 20.788|

sad_value2(7) |min_num(8) | 20.568|

sad_value2(7) |min_num(9) | 20.437|

sad_value2(7) |position(0) | 19.522|

sad_value2(7) |position(1) | 20.176|

sad_value2(7) |position(2) | 19.327|

sad_value2(8) |min_num(0) | 20.774|

sad_value2(8) |min_num(1) | 20.259|

sad_value2(8) |min_num(10) | 20.422|

sad_value2(8) |min_num(11) | 21.065|

sad_value2(8) |min_num(2) | 20.391|

sad_value2(8) |min_num(3) | 20.243|

sad_value2(8) |min_num(4) | 21.353|

sad_value2(8) |min_num(5) | 21.298|

sad_value2(8) |min_num(6) | 21.082|

sad_value2(8) |min_num(7) | 21.382|

sad_value2(8) |min_num(8) | 21.162|

sad_value2(8) |min_num(9) | 21.031|

sad_value2(8) |position(0) | 20.116|

sad_value2(8) |position(1) | 20.770|

sad_value2(8) |position(2) | 19.921|

sad_value2(9) |min_num(0) | 20.428|

sad_value2(9) |min_num(1) | 19.913|

sad_value2(9) |min_num(10) | 20.076|

sad_value2(9) |min_num(11) | 20.719|

sad_value2(9) |min_num(2) | 20.045|

sad_value2(9) |min_num(3) | 19.897|

sad_value2(9) |min_num(4) | 21.007|

sad_value2(9) |min_num(5) | 20.952|

sad_value2(9) |min_num(6) | 20.736|

sad_value2(9) |min_num(7) | 21.036|

sad_value2(9) |min_num(8) | 20.816|

sad_value2(9) |min_num(9) | 20.685|

sad_value2(9) |position(0) | 19.770|

sad_value2(9) |position(1) | 20.424|

sad_value2(9) |position(2) | 19.575|

sad_value3(0) |min_num(0) | 21.592|

sad_value3(0) |min_num(1) | 21.077|

sad_value3(0) |min_num(10) | 21.240|

sad_value3(0) |min_num(11) | 21.883|

sad_value3(0) |min_num(2) | 21.209|

sad_value3(0) |min_num(3) | 21.061|

sad_value3(0) |min_num(4) | 22.171|

sad_value3(0) |min_num(5) | 22.116|

sad_value3(0) |min_num(6) | 21.900|

sad_value3(0) |min_num(7) | 22.200|

sad_value3(0) |min_num(8) | 21.980|

sad_value3(0) |min_num(9) | 21.849|

sad_value3(0) |position(0) | 20.934|

sad_value3(0) |position(1) | 21.588|

sad_value3(0) |position(2) | 20.739|

sad_value3(1) |min_num(0) | 21.092|

sad_value3(1) |min_num(1) | 20.577|

sad_value3(1) |min_num(10) | 20.740|

sad_value3(1) |min_num(11) | 21.383|

sad_value3(1) |min_num(2) | 20.709|

sad_value3(1) |min_num(3) | 20.561|

sad_value3(1) |min_num(4) | 21.671|

sad_value3(1) |min_num(5) | 21.616|

sad_value3(1) |min_num(6) | 21.400|

sad_value3(1) |min_num(7) | 21.700|

sad_value3(1) |min_num(8) | 21.480|

sad_value3(1) |min_num(9) | 21.349|

sad_value3(1) |position(0) | 20.434|

sad_value3(1) |position(1) | 21.088|

sad_value3(1) |position(2) | 20.239|

sad_value3(10) |min_num(0) | 21.593|

sad_value3(10) |min_num(1) | 21.078|

sad_value3(10) |min_num(10) | 21.241|

sad_value3(10) |min_num(11) | 21.884|

sad_value3(10) |min_num(2) | 21.210|

sad_value3(10) |min_num(3) | 21.062|

sad_value3(10) |min_num(4) | 22.172|

sad_value3(10) |min_num(5) | 22.117|

sad_value3(10) |min_num(6) | 21.901|

sad_value3(10) |min_num(7) | 22.201|

sad_value3(10) |min_num(8) | 21.981|

sad_value3(10) |min_num(9) | 21.850|

sad_value3(10) |position(0) | 20.935|

sad_value3(10) |position(1) | 21.589|

sad_value3(10) |position(2) | 20.740|

sad_value3(11) |min_num(0) | 21.410|

sad_value3(11) |min_num(1) | 20.895|

sad_value3(11) |min_num(10) | 21.058|

sad_value3(11) |min_num(11) | 21.701|

sad_value3(11) |min_num(2) | 21.027|

sad_value3(11) |min_num(3) | 20.879|

sad_value3(11) |min_num(4) | 21.989|

sad_value3(11) |min_num(5) | 21.934|

sad_value3(11) |min_num(6) | 21.718|

sad_value3(11) |min_num(7) | 22.018|

sad_value3(11) |min_num(8) | 21.798|

sad_value3(11) |min_num(9) | 21.667|

sad_value3(11) |position(0) | 20.752|

sad_value3(11) |position(1) | 21.406|

sad_value3(11) |position(2) | 20.557|

sad_value3(2) |min_num(0) | 21.823|

sad_value3(2) |min_num(1) | 21.308|

sad_value3(2) |min_num(10) | 21.471|

sad_value3(2) |min_num(11) | 22.114|

sad_value3(2) |min_num(2) | 21.440|

sad_value3(2) |min_num(3) | 21.292|

sad_value3(2) |min_num(4) | 22.402|

sad_value3(2) |min_num(5) | 22.347|

sad_value3(2) |min_num(6) | 22.131|

sad_value3(2) |min_num(7) | 22.431|

sad_value3(2) |min_num(8) | 22.211|

sad_value3(2) |min_num(9) | 22.080|

sad_value3(2) |position(0) | 21.165|

sad_value3(2) |position(1) | 21.819|

sad_value3(2) |position(2) | 20.970|

sad_value3(3) |min_num(0) | 21.221|

sad_value3(3) |min_num(1) | 20.706|

sad_value3(3) |min_num(10) | 20.869|

sad_value3(3) |min_num(11) | 21.512|

sad_value3(3) |min_num(2) | 20.838|

sad_value3(3) |min_num(3) | 20.690|

sad_value3(3) |min_num(4) | 21.800|

sad_value3(3) |min_num(5) | 21.745|

sad_value3(3) |min_num(6) | 21.529|

sad_value3(3) |min_num(7) | 21.829|

sad_value3(3) |min_num(8) | 21.609|

sad_value3(3) |min_num(9) | 21.478|

sad_value3(3) |position(0) | 20.563|

sad_value3(3) |position(1) | 21.217|

sad_value3(3) |position(2) | 20.368|

sad_value3(4) |min_num(0) | 21.262|

sad_value3(4) |min_num(1) | 20.747|

sad_value3(4) |min_num(10) | 20.910|

sad_value3(4) |min_num(11) | 21.553|

sad_value3(4) |min_num(2) | 20.879|

sad_value3(4) |min_num(3) | 20.731|

sad_value3(4) |min_num(4) | 21.841|

sad_value3(4) |min_num(5) | 21.786|

sad_value3(4) |min_num(6) | 21.570|

sad_value3(4) |min_num(7) | 21.870|

sad_value3(4) |min_num(8) | 21.650|

sad_value3(4) |min_num(9) | 21.519|

sad_value3(4) |position(0) | 20.604|

sad_value3(4) |position(1) | 21.258|

sad_value3(4) |position(2) | 20.409|

sad_value3(5) |min_num(0) | 22.087|

sad_value3(5) |min_num(1) | 21.572|

sad_value3(5) |min_num(10) | 21.735|

sad_value3(5) |min_num(11) | 22.378|

sad_value3(5) |min_num(2) | 21.704|

sad_value3(5) |min_num(3) | 21.556|

sad_value3(5) |min_num(4) | 22.666|

sad_value3(5) |min_num(5) | 22.611|

sad_value3(5) |min_num(6) | 22.395|

sad_value3(5) |min_num(7) | 22.695|

sad_value3(5) |min_num(8) | 22.475|

sad_value3(5) |min_num(9) | 22.344|

sad_value3(5) |position(0) | 21.429|

sad_value3(5) |position(1) | 22.083|

sad_value3(5) |position(2) | 21.234|

sad_value3(6) |min_num(0) | 21.574|

sad_value3(6) |min_num(1) | 21.059|

sad_value3(6) |min_num(10) | 21.222|

sad_value3(6) |min_num(11) | 21.865|

sad_value3(6) |min_num(2) | 21.191|

sad_value3(6) |min_num(3) | 21.043|

sad_value3(6) |min_num(4) | 22.153|

sad_value3(6) |min_num(5) | 22.098|

sad_value3(6) |min_num(6) | 21.882|

sad_value3(6) |min_num(7) | 22.182|

sad_value3(6) |min_num(8) | 21.962|

sad_value3(6) |min_num(9) | 21.831|

sad_value3(6) |position(0) | 20.916|

sad_value3(6) |position(1) | 21.570|

sad_value3(6) |position(2) | 20.721|

sad_value3(7) |min_num(0) | 21.142|

sad_value3(7) |min_num(1) | 20.627|

sad_value3(7) |min_num(10) | 20.790|

sad_value3(7) |min_num(11) | 21.433|

sad_value3(7) |min_num(2) | 20.759|

sad_value3(7) |min_num(3) | 20.611|

sad_value3(7) |min_num(4) | 21.721|

sad_value3(7) |min_num(5) | 21.666|

sad_value3(7) |min_num(6) | 21.450|

sad_value3(7) |min_num(7) | 21.750|

sad_value3(7) |min_num(8) | 21.530|

sad_value3(7) |min_num(9) | 21.399|

sad_value3(7) |position(0) | 20.484|

sad_value3(7) |position(1) | 21.138|

sad_value3(7) |position(2) | 20.289|

sad_value3(8) |min_num(0) | 21.799|

sad_value3(8) |min_num(1) | 21.284|

sad_value3(8) |min_num(10) | 21.447|

sad_value3(8) |min_num(11) | 22.090|

sad_value3(8) |min_num(2) | 21.416|

sad_value3(8) |min_num(3) | 21.268|

sad_value3(8) |min_num(4) | 22.378|

sad_value3(8) |min_num(5) | 22.323|

sad_value3(8) |min_num(6) | 22.107|

sad_value3(8) |min_num(7) | 22.407|

sad_value3(8) |min_num(8) | 22.187|

sad_value3(8) |min_num(9) | 22.056|

sad_value3(8) |position(0) | 21.141|

sad_value3(8) |position(1) | 21.795|

sad_value3(8) |position(2) | 20.946|

sad_value3(9) |min_num(0) | 21.397|

sad_value3(9) |min_num(1) | 20.882|

sad_value3(9) |min_num(10) | 21.045|

sad_value3(9) |min_num(11) | 21.688|

sad_value3(9) |min_num(2) | 21.014|

sad_value3(9) |min_num(3) | 20.866|

sad_value3(9) |min_num(4) | 21.976|

sad_value3(9) |min_num(5) | 21.921|

sad_value3(9) |min_num(6) | 21.705|

sad_value3(9) |min_num(7) | 22.005|

sad_value3(9) |min_num(8) | 21.785|

sad_value3(9) |min_num(9) | 21.654|

sad_value3(9) |position(0) | 20.739|

sad_value3(9) |position(1) | 21.393|

sad_value3(9) |position(2) | 20.544|

sad_value4(0) |min_num(0) | 21.979|

sad_value4(0) |min_num(1) | 21.464|

sad_value4(0) |min_num(10) | 21.627|

sad_value4(0) |min_num(11) | 22.270|

sad_value4(0) |min_num(2) | 21.596|

sad_value4(0) |min_num(3) | 21.448|

sad_value4(0) |min_num(4) | 22.558|

sad_value4(0) |min_num(5) | 22.503|

sad_value4(0) |min_num(6) | 22.287|

sad_value4(0) |min_num(7) | 22.587|

sad_value4(0) |min_num(8) | 22.367|

sad_value4(0) |min_num(9) | 22.236|

sad_value4(0) |position(0) | 21.321|

sad_value4(0) |position(1) | 21.975|

sad_value4(0) |position(2) | 21.126|

sad_value4(1) |min_num(0) | 21.717|

sad_value4(1) |min_num(1) | 21.202|

sad_value4(1) |min_num(10) | 21.365|

sad_value4(1) |min_num(11) | 22.008|

sad_value4(1) |min_num(2) | 21.334|

sad_value4(1) |min_num(3) | 21.186|

sad_value4(1) |min_num(4) | 22.296|

sad_value4(1) |min_num(5) | 22.241|

sad_value4(1) |min_num(6) | 22.025|

sad_value4(1) |min_num(7) | 22.325|

sad_value4(1) |min_num(8) | 22.105|

sad_value4(1) |min_num(9) | 21.974|

sad_value4(1) |position(0) | 21.059|

sad_value4(1) |position(1) | 21.713|

sad_value4(1) |position(2) | 20.864|

sad_value4(10) |min_num(0) | 21.609|

sad_value4(10) |min_num(1) | 21.094|

sad_value4(10) |min_num(10) | 21.257|

sad_value4(10) |min_num(11) | 21.900|

sad_value4(10) |min_num(2) | 21.226|

sad_value4(10) |min_num(3) | 21.078|

sad_value4(10) |min_num(4) | 22.188|

sad_value4(10) |min_num(5) | 22.133|

sad_value4(10) |min_num(6) | 21.917|

sad_value4(10) |min_num(7) | 22.217|

sad_value4(10) |min_num(8) | 21.997|

sad_value4(10) |min_num(9) | 21.866|

sad_value4(10) |position(0) | 20.951|

sad_value4(10) |position(1) | 21.605|

sad_value4(10) |position(2) | 20.756|

sad_value4(11) |min_num(0) | 21.378|

sad_value4(11) |min_num(1) | 20.863|

sad_value4(11) |min_num(10) | 21.026|

sad_value4(11) |min_num(11) | 21.669|

sad_value4(11) |min_num(2) | 20.995|

sad_value4(11) |min_num(3) | 20.847|

sad_value4(11) |min_num(4) | 21.957|

sad_value4(11) |min_num(5) | 21.902|

sad_value4(11) |min_num(6) | 21.686|

sad_value4(11) |min_num(7) | 21.986|

sad_value4(11) |min_num(8) | 21.766|

sad_value4(11) |min_num(9) | 21.635|

sad_value4(11) |position(0) | 20.720|

sad_value4(11) |position(1) | 21.374|

sad_value4(11) |position(2) | 20.525|

sad_value4(2) |min_num(0) | 21.449|

sad_value4(2) |min_num(1) | 20.934|

sad_value4(2) |min_num(10) | 21.097|

sad_value4(2) |min_num(11) | 21.740|

sad_value4(2) |min_num(2) | 21.066|

sad_value4(2) |min_num(3) | 20.918|

sad_value4(2) |min_num(4) | 22.028|

sad_value4(2) |min_num(5) | 21.973|

sad_value4(2) |min_num(6) | 21.757|

sad_value4(2) |min_num(7) | 22.057|

sad_value4(2) |min_num(8) | 21.837|

sad_value4(2) |min_num(9) | 21.706|

sad_value4(2) |position(0) | 20.791|

sad_value4(2) |position(1) | 21.445|

sad_value4(2) |position(2) | 20.596|

sad_value4(3) |min_num(0) | 21.439|

sad_value4(3) |min_num(1) | 20.924|

sad_value4(3) |min_num(10) | 21.087|

sad_value4(3) |min_num(11) | 21.730|

sad_value4(3) |min_num(2) | 21.056|

sad_value4(3) |min_num(3) | 20.908|

sad_value4(3) |min_num(4) | 22.018|

sad_value4(3) |min_num(5) | 21.963|

sad_value4(3) |min_num(6) | 21.747|

sad_value4(3) |min_num(7) | 22.047|

sad_value4(3) |min_num(8) | 21.827|

sad_value4(3) |min_num(9) | 21.696|

sad_value4(3) |position(0) | 20.781|

sad_value4(3) |position(1) | 21.435|

sad_value4(3) |position(2) | 20.586|

sad_value4(4) |min_num(0) | 21.675|

sad_value4(4) |min_num(1) | 21.160|

sad_value4(4) |min_num(10) | 21.323|

sad_value4(4) |min_num(11) | 21.966|

sad_value4(4) |min_num(2) | 21.292|

sad_value4(4) |min_num(3) | 21.144|

sad_value4(4) |min_num(4) | 22.254|

sad_value4(4) |min_num(5) | 22.199|

sad_value4(4) |min_num(6) | 21.983|

sad_value4(4) |min_num(7) | 22.283|

sad_value4(4) |min_num(8) | 22.063|

sad_value4(4) |min_num(9) | 21.932|

sad_value4(4) |position(0) | 21.017|

sad_value4(4) |position(1) | 21.671|

sad_value4(4) |position(2) | 20.822|

sad_value4(5) |min_num(0) | 21.039|

sad_value4(5) |min_num(1) | 20.524|

sad_value4(5) |min_num(10) | 20.687|

sad_value4(5) |min_num(11) | 21.330|

sad_value4(5) |min_num(2) | 20.656|

sad_value4(5) |min_num(3) | 20.508|

sad_value4(5) |min_num(4) | 21.618|

sad_value4(5) |min_num(5) | 21.563|

sad_value4(5) |min_num(6) | 21.347|

sad_value4(5) |min_num(7) | 21.647|

sad_value4(5) |min_num(8) | 21.427|

sad_value4(5) |min_num(9) | 21.296|

sad_value4(5) |position(0) | 20.381|

sad_value4(5) |position(1) | 21.035|

sad_value4(5) |position(2) | 20.186|

sad_value4(6) |min_num(0) | 21.730|

sad_value4(6) |min_num(1) | 21.215|

sad_value4(6) |min_num(10) | 21.378|

sad_value4(6) |min_num(11) | 22.021|

sad_value4(6) |min_num(2) | 21.347|

sad_value4(6) |min_num(3) | 21.199|

sad_value4(6) |min_num(4) | 22.309|

sad_value4(6) |min_num(5) | 22.254|

sad_value4(6) |min_num(6) | 22.038|

sad_value4(6) |min_num(7) | 22.338|

sad_value4(6) |min_num(8) | 22.118|

sad_value4(6) |min_num(9) | 21.987|

sad_value4(6) |position(0) | 21.072|

sad_value4(6) |position(1) | 21.726|

sad_value4(6) |position(2) | 20.877|

sad_value4(7) |min_num(0) | 21.399|

sad_value4(7) |min_num(1) | 20.884|

sad_value4(7) |min_num(10) | 21.047|

sad_value4(7) |min_num(11) | 21.690|

sad_value4(7) |min_num(2) | 21.016|

sad_value4(7) |min_num(3) | 20.868|

sad_value4(7) |min_num(4) | 21.978|

sad_value4(7) |min_num(5) | 21.923|

sad_value4(7) |min_num(6) | 21.707|

sad_value4(7) |min_num(7) | 22.007|

sad_value4(7) |min_num(8) | 21.787|

sad_value4(7) |min_num(9) | 21.656|

sad_value4(7) |position(0) | 20.741|

sad_value4(7) |position(1) | 21.395|

sad_value4(7) |position(2) | 20.546|

sad_value4(8) |min_num(0) | 21.741|

sad_value4(8) |min_num(1) | 21.226|

sad_value4(8) |min_num(10) | 21.389|

sad_value4(8) |min_num(11) | 22.032|

sad_value4(8) |min_num(2) | 21.358|

sad_value4(8) |min_num(3) | 21.210|

sad_value4(8) |min_num(4) | 22.320|

sad_value4(8) |min_num(5) | 22.265|

sad_value4(8) |min_num(6) | 22.049|

sad_value4(8) |min_num(7) | 22.349|

sad_value4(8) |min_num(8) | 22.129|

sad_value4(8) |min_num(9) | 21.998|

sad_value4(8) |position(0) | 21.083|

sad_value4(8) |position(1) | 21.737|

sad_value4(8) |position(2) | 20.888|

sad_value4(9) |min_num(0) | 21.597|

sad_value4(9) |min_num(1) | 21.082|

sad_value4(9) |min_num(10) | 21.245|

sad_value4(9) |min_num(11) | 21.888|

sad_value4(9) |min_num(2) | 21.214|

sad_value4(9) |min_num(3) | 21.066|

sad_value4(9) |min_num(4) | 22.176|

sad_value4(9) |min_num(5) | 22.121|

sad_value4(9) |min_num(6) | 21.905|

sad_value4(9) |min_num(7) | 22.205|

sad_value4(9) |min_num(8) | 21.985|

sad_value4(9) |min_num(9) | 21.854|

sad_value4(9) |position(0) | 20.939|

sad_value4(9) |position(1) | 21.593|

sad_value4(9) |position(2) | 20.744|

sad_value5(0) |min_num(0) | 20.376|

sad_value5(0) |min_num(1) | 19.861|

sad_value5(0) |min_num(10) | 20.024|

sad_value5(0) |min_num(11) | 20.667|

sad_value5(0) |min_num(2) | 19.993|

sad_value5(0) |min_num(3) | 19.845|

sad_value5(0) |min_num(4) | 20.955|

sad_value5(0) |min_num(5) | 20.900|

sad_value5(0) |min_num(6) | 20.684|

sad_value5(0) |min_num(7) | 20.984|

sad_value5(0) |min_num(8) | 20.764|

sad_value5(0) |min_num(9) | 20.633|

sad_value5(0) |position(0) | 19.718|

sad_value5(0) |position(1) | 20.372|

sad_value5(0) |position(2) | 19.523|

sad_value5(1) |min_num(0) | 20.577|

sad_value5(1) |min_num(1) | 20.062|

sad_value5(1) |min_num(10) | 20.225|

sad_value5(1) |min_num(11) | 20.868|

sad_value5(1) |min_num(2) | 20.194|

sad_value5(1) |min_num(3) | 20.046|

sad_value5(1) |min_num(4) | 21.156|

sad_value5(1) |min_num(5) | 21.101|

sad_value5(1) |min_num(6) | 20.885|

sad_value5(1) |min_num(7) | 21.185|

sad_value5(1) |min_num(8) | 20.965|

sad_value5(1) |min_num(9) | 20.834|

sad_value5(1) |position(0) | 19.919|

sad_value5(1) |position(1) | 20.573|

sad_value5(1) |position(2) | 19.724|

sad_value5(10) |min_num(0) | 20.448|

sad_value5(10) |min_num(1) | 19.933|

sad_value5(10) |min_num(10) | 20.096|

sad_value5(10) |min_num(11) | 20.739|

sad_value5(10) |min_num(2) | 20.065|

sad_value5(10) |min_num(3) | 19.917|

sad_value5(10) |min_num(4) | 21.027|

sad_value5(10) |min_num(5) | 20.972|

sad_value5(10) |min_num(6) | 20.756|

sad_value5(10) |min_num(7) | 21.056|

sad_value5(10) |min_num(8) | 20.836|

sad_value5(10) |min_num(9) | 20.705|

sad_value5(10) |position(0) | 19.790|

sad_value5(10) |position(1) | 20.444|

sad_value5(10) |position(2) | 19.595|

sad_value5(11) |min_num(0) | 20.227|

sad_value5(11) |min_num(1) | 19.712|

sad_value5(11) |min_num(10) | 19.875|

sad_value5(11) |min_num(11) | 20.518|

sad_value5(11) |min_num(2) | 19.844|

sad_value5(11) |min_num(3) | 19.696|

sad_value5(11) |min_num(4) | 20.806|

sad_value5(11) |min_num(5) | 20.751|

sad_value5(11) |min_num(6) | 20.535|

sad_value5(11) |min_num(7) | 20.835|

sad_value5(11) |min_num(8) | 20.615|

sad_value5(11) |min_num(9) | 20.484|

sad_value5(11) |position(0) | 19.569|

sad_value5(11) |position(1) | 20.223|

sad_value5(11) |position(2) | 19.374|

sad_value5(2) |min_num(0) | 20.712|

sad_value5(2) |min_num(1) | 20.197|

sad_value5(2) |min_num(10) | 20.360|

sad_value5(2) |min_num(11) | 21.003|

sad_value5(2) |min_num(2) | 20.329|

sad_value5(2) |min_num(3) | 20.181|

sad_value5(2) |min_num(4) | 21.291|

sad_value5(2) |min_num(5) | 21.236|

sad_value5(2) |min_num(6) | 21.020|

sad_value5(2) |min_num(7) | 21.320|

sad_value5(2) |min_num(8) | 21.100|

sad_value5(2) |min_num(9) | 20.969|

sad_value5(2) |position(0) | 20.054|

sad_value5(2) |position(1) | 20.708|

sad_value5(2) |position(2) | 19.859|

sad_value5(3) |min_num(0) | 20.549|

sad_value5(3) |min_num(1) | 20.034|

sad_value5(3) |min_num(10) | 20.197|

sad_value5(3) |min_num(11) | 20.840|

sad_value5(3) |min_num(2) | 20.166|

sad_value5(3) |min_num(3) | 20.018|

sad_value5(3) |min_num(4) | 21.128|

sad_value5(3) |min_num(5) | 21.073|

sad_value5(3) |min_num(6) | 20.857|

sad_value5(3) |min_num(7) | 21.157|

sad_value5(3) |min_num(8) | 20.937|

sad_value5(3) |min_num(9) | 20.806|

sad_value5(3) |position(0) | 19.891|

sad_value5(3) |position(1) | 20.545|

sad_value5(3) |position(2) | 19.696|

sad_value5(4) |min_num(0) | 20.340|

sad_value5(4) |min_num(1) | 19.825|

sad_value5(4) |min_num(10) | 19.988|

sad_value5(4) |min_num(11) | 20.631|

sad_value5(4) |min_num(2) | 19.957|

sad_value5(4) |min_num(3) | 19.809|

sad_value5(4) |min_num(4) | 20.919|

sad_value5(4) |min_num(5) | 20.864|

sad_value5(4) |min_num(6) | 20.648|

sad_value5(4) |min_num(7) | 20.948|

sad_value5(4) |min_num(8) | 20.728|

sad_value5(4) |min_num(9) | 20.597|

sad_value5(4) |position(0) | 19.682|

sad_value5(4) |position(1) | 20.336|

sad_value5(4) |position(2) | 19.487|

sad_value5(5) |min_num(0) | 20.717|

sad_value5(5) |min_num(1) | 20.202|

sad_value5(5) |min_num(10) | 20.365|

sad_value5(5) |min_num(11) | 21.008|

sad_value5(5) |min_num(2) | 20.334|

sad_value5(5) |min_num(3) | 20.186|

sad_value5(5) |min_num(4) | 21.296|

sad_value5(5) |min_num(5) | 21.241|

sad_value5(5) |min_num(6) | 21.025|

sad_value5(5) |min_num(7) | 21.325|

sad_value5(5) |min_num(8) | 21.105|

sad_value5(5) |min_num(9) | 20.974|

sad_value5(5) |position(0) | 20.059|

sad_value5(5) |position(1) | 20.713|

sad_value5(5) |position(2) | 19.864|

sad_value5(6) |min_num(0) | 20.792|

sad_value5(6) |min_num(1) | 20.277|

sad_value5(6) |min_num(10) | 20.440|

sad_value5(6) |min_num(11) | 21.083|

sad_value5(6) |min_num(2) | 20.409|

sad_value5(6) |min_num(3) | 20.261|

sad_value5(6) |min_num(4) | 21.371|

sad_value5(6) |min_num(5) | 21.316|

sad_value5(6) |min_num(6) | 21.100|

sad_value5(6) |min_num(7) | 21.400|

sad_value5(6) |min_num(8) | 21.180|

sad_value5(6) |min_num(9) | 21.049|

sad_value5(6) |position(0) | 20.134|

sad_value5(6) |position(1) | 20.788|

sad_value5(6) |position(2) | 19.939|

sad_value5(7) |min_num(0) | 20.927|

sad_value5(7) |min_num(1) | 20.412|

sad_value5(7) |min_num(10) | 20.575|

sad_value5(7) |min_num(11) | 21.218|

sad_value5(7) |min_num(2) | 20.544|

sad_value5(7) |min_num(3) | 20.396|

sad_value5(7) |min_num(4) | 21.506|

sad_value5(7) |min_num(5) | 21.451|

sad_value5(7) |min_num(6) | 21.235|

sad_value5(7) |min_num(7) | 21.535|

sad_value5(7) |min_num(8) | 21.315|

sad_value5(7) |min_num(9) | 21.184|

sad_value5(7) |position(0) | 20.269|

sad_value5(7) |position(1) | 20.923|

sad_value5(7) |position(2) | 20.074|

sad_value5(8) |min_num(0) | 20.678|

sad_value5(8) |min_num(1) | 20.163|

sad_value5(8) |min_num(10) | 20.326|

sad_value5(8) |min_num(11) | 20.969|

sad_value5(8) |min_num(2) | 20.295|

sad_value5(8) |min_num(3) | 20.147|

sad_value5(8) |min_num(4) | 21.257|

sad_value5(8) |min_num(5) | 21.202|

sad_value5(8) |min_num(6) | 20.986|

sad_value5(8) |min_num(7) | 21.286|

sad_value5(8) |min_num(8) | 21.066|

sad_value5(8) |min_num(9) | 20.935|

sad_value5(8) |position(0) | 20.020|

sad_value5(8) |position(1) | 20.674|

sad_value5(8) |position(2) | 19.825|

sad_value5(9) |min_num(0) | 20.322|

sad_value5(9) |min_num(1) | 19.807|

sad_value5(9) |min_num(10) | 19.970|

sad_value5(9) |min_num(11) | 20.613|

sad_value5(9) |min_num(2) | 19.939|

sad_value5(9) |min_num(3) | 19.791|

sad_value5(9) |min_num(4) | 20.901|

sad_value5(9) |min_num(5) | 20.846|

sad_value5(9) |min_num(6) | 20.630|

sad_value5(9) |min_num(7) | 20.930|

sad_value5(9) |min_num(8) | 20.710|

sad_value5(9) |min_num(9) | 20.579|

sad_value5(9) |position(0) | 19.664|

sad_value5(9) |position(1) | 20.318|

sad_value5(9) |position(2) | 19.469|

sad_value6(0) |min_num(0) | 19.524|

sad_value6(0) |min_num(1) | 19.009|

sad_value6(0) |min_num(10) | 19.172|

sad_value6(0) |min_num(11) | 19.815|

sad_value6(0) |min_num(2) | 19.141|

sad_value6(0) |min_num(3) | 18.993|

sad_value6(0) |min_num(4) | 20.103|

sad_value6(0) |min_num(5) | 20.048|

sad_value6(0) |min_num(6) | 19.832|

sad_value6(0) |min_num(7) | 20.132|

sad_value6(0) |min_num(8) | 19.912|

sad_value6(0) |min_num(9) | 19.781|

sad_value6(0) |position(0) | 18.866|

sad_value6(0) |position(1) | 19.520|

sad_value6(0) |position(2) | 18.671|

sad_value6(1) |min_num(0) | 19.426|

sad_value6(1) |min_num(1) | 18.911|

sad_value6(1) |min_num(10) | 19.074|

sad_value6(1) |min_num(11) | 19.717|

sad_value6(1) |min_num(2) | 19.043|

sad_value6(1) |min_num(3) | 18.895|

sad_value6(1) |min_num(4) | 20.005|

sad_value6(1) |min_num(5) | 19.950|

sad_value6(1) |min_num(6) | 19.734|

sad_value6(1) |min_num(7) | 20.034|

sad_value6(1) |min_num(8) | 19.814|

sad_value6(1) |min_num(9) | 19.683|

sad_value6(1) |position(0) | 18.768|

sad_value6(1) |position(1) | 19.422|

sad_value6(1) |position(2) | 18.573|

sad_value6(10) |min_num(0) | 19.125|

sad_value6(10) |min_num(1) | 18.610|

sad_value6(10) |min_num(10) | 18.773|

sad_value6(10) |min_num(11) | 19.416|

sad_value6(10) |min_num(2) | 18.742|

sad_value6(10) |min_num(3) | 18.594|

sad_value6(10) |min_num(4) | 19.704|

sad_value6(10) |min_num(5) | 19.649|

sad_value6(10) |min_num(6) | 19.433|

sad_value6(10) |min_num(7) | 19.733|

sad_value6(10) |min_num(8) | 19.513|

sad_value6(10) |min_num(9) | 19.382|

sad_value6(10) |position(0) | 18.467|

sad_value6(10) |position(1) | 19.121|

sad_value6(10) |position(2) | 18.272|

sad_value6(11) |min_num(0) | 19.252|

sad_value6(11) |min_num(1) | 18.737|

sad_value6(11) |min_num(10) | 18.900|

sad_value6(11) |min_num(11) | 19.543|

sad_value6(11) |min_num(2) | 18.869|

sad_value6(11) |min_num(3) | 18.721|

sad_value6(11) |min_num(4) | 19.831|

sad_value6(11) |min_num(5) | 19.776|

sad_value6(11) |min_num(6) | 19.560|

sad_value6(11) |min_num(7) | 19.860|

sad_value6(11) |min_num(8) | 19.640|

sad_value6(11) |min_num(9) | 19.509|

sad_value6(11) |position(0) | 18.594|

sad_value6(11) |position(1) | 19.248|

sad_value6(11) |position(2) | 18.399|

sad_value6(2) |min_num(0) | 19.562|

sad_value6(2) |min_num(1) | 19.047|

sad_value6(2) |min_num(10) | 19.210|

sad_value6(2) |min_num(11) | 19.853|

sad_value6(2) |min_num(2) | 19.179|

sad_value6(2) |min_num(3) | 19.031|

sad_value6(2) |min_num(4) | 20.141|

sad_value6(2) |min_num(5) | 20.086|

sad_value6(2) |min_num(6) | 19.870|

sad_value6(2) |min_num(7) | 20.170|

sad_value6(2) |min_num(8) | 19.950|

sad_value6(2) |min_num(9) | 19.819|

sad_value6(2) |position(0) | 18.904|

sad_value6(2) |position(1) | 19.558|

sad_value6(2) |position(2) | 18.709|

sad_value6(3) |min_num(0) | 19.756|

sad_value6(3) |min_num(1) | 19.241|

sad_value6(3) |min_num(10) | 19.404|

sad_value6(3) |min_num(11) | 20.047|

sad_value6(3) |min_num(2) | 19.373|

sad_value6(3) |min_num(3) | 19.225|

sad_value6(3) |min_num(4) | 20.335|

sad_value6(3) |min_num(5) | 20.280|

sad_value6(3) |min_num(6) | 20.064|

sad_value6(3) |min_num(7) | 20.364|

sad_value6(3) |min_num(8) | 20.144|

sad_value6(3) |min_num(9) | 20.013|

sad_value6(3) |position(0) | 19.098|

sad_value6(3) |position(1) | 19.752|

sad_value6(3) |position(2) | 18.903|

sad_value6(4) |min_num(0) | 19.663|

sad_value6(4) |min_num(1) | 19.148|

sad_value6(4) |min_num(10) | 19.311|

sad_value6(4) |min_num(11) | 19.954|

sad_value6(4) |min_num(2) | 19.280|

sad_value6(4) |min_num(3) | 19.132|

sad_value6(4) |min_num(4) | 20.242|

sad_value6(4) |min_num(5) | 20.187|

sad_value6(4) |min_num(6) | 19.971|

sad_value6(4) |min_num(7) | 20.271|

sad_value6(4) |min_num(8) | 20.051|

sad_value6(4) |min_num(9) | 19.920|

sad_value6(4) |position(0) | 19.005|

sad_value6(4) |position(1) | 19.659|

sad_value6(4) |position(2) | 18.810|

sad_value6(5) |min_num(0) | 20.194|

sad_value6(5) |min_num(1) | 19.679|

sad_value6(5) |min_num(10) | 19.842|

sad_value6(5) |min_num(11) | 20.485|

sad_value6(5) |min_num(2) | 19.811|

sad_value6(5) |min_num(3) | 19.663|

sad_value6(5) |min_num(4) | 20.773|

sad_value6(5) |min_num(5) | 20.718|

sad_value6(5) |min_num(6) | 20.502|

sad_value6(5) |min_num(7) | 20.802|

sad_value6(5) |min_num(8) | 20.582|

sad_value6(5) |min_num(9) | 20.451|

sad_value6(5) |position(0) | 19.536|

sad_value6(5) |position(1) | 20.190|

sad_value6(5) |position(2) | 19.341|

sad_value6(6) |min_num(0) | 19.437|

sad_value6(6) |min_num(1) | 18.922|

sad_value6(6) |min_num(10) | 19.085|

sad_value6(6) |min_num(11) | 19.728|

sad_value6(6) |min_num(2) | 19.054|

sad_value6(6) |min_num(3) | 18.906|

sad_value6(6) |min_num(4) | 20.016|

sad_value6(6) |min_num(5) | 19.961|

sad_value6(6) |min_num(6) | 19.745|

sad_value6(6) |min_num(7) | 20.045|

sad_value6(6) |min_num(8) | 19.825|

sad_value6(6) |min_num(9) | 19.694|

sad_value6(6) |position(0) | 18.779|

sad_value6(6) |position(1) | 19.433|

sad_value6(6) |position(2) | 18.584|

sad_value6(7) |min_num(0) | 19.871|

sad_value6(7) |min_num(1) | 19.356|

sad_value6(7) |min_num(10) | 19.519|

sad_value6(7) |min_num(11) | 20.162|

sad_value6(7) |min_num(2) | 19.488|

sad_value6(7) |min_num(3) | 19.340|

sad_value6(7) |min_num(4) | 20.450|

sad_value6(7) |min_num(5) | 20.395|

sad_value6(7) |min_num(6) | 20.179|

sad_value6(7) |min_num(7) | 20.479|

sad_value6(7) |min_num(8) | 20.259|

sad_value6(7) |min_num(9) | 20.128|

sad_value6(7) |position(0) | 19.213|

sad_value6(7) |position(1) | 19.867|

sad_value6(7) |position(2) | 19.018|

sad_value6(8) |min_num(0) | 19.329|

sad_value6(8) |min_num(1) | 18.814|

sad_value6(8) |min_num(10) | 18.977|

sad_value6(8) |min_num(11) | 19.620|

sad_value6(8) |min_num(2) | 18.946|

sad_value6(8) |min_num(3) | 18.798|

sad_value6(8) |min_num(4) | 19.908|

sad_value6(8) |min_num(5) | 19.853|

sad_value6(8) |min_num(6) | 19.637|

sad_value6(8) |min_num(7) | 19.937|

sad_value6(8) |min_num(8) | 19.717|

sad_value6(8) |min_num(9) | 19.586|

sad_value6(8) |position(0) | 18.671|

sad_value6(8) |position(1) | 19.325|

sad_value6(8) |position(2) | 18.476|

sad_value6(9) |min_num(0) | 19.369|

sad_value6(9) |min_num(1) | 18.854|

sad_value6(9) |min_num(10) | 19.017|

sad_value6(9) |min_num(11) | 19.660|

sad_value6(9) |min_num(2) | 18.986|

sad_value6(9) |min_num(3) | 18.838|

sad_value6(9) |min_num(4) | 19.948|

sad_value6(9) |min_num(5) | 19.893|

sad_value6(9) |min_num(6) | 19.677|

sad_value6(9) |min_num(7) | 19.977|

sad_value6(9) |min_num(8) | 19.757|

sad_value6(9) |min_num(9) | 19.626|

sad_value6(9) |position(0) | 18.711|

sad_value6(9) |position(1) | 19.365|

sad_value6(9) |position(2) | 18.516|

sad_value7(0) |min_num(0) | 18.661|

sad_value7(0) |min_num(1) | 18.146|

sad_value7(0) |min_num(10) | 18.309|

sad_value7(0) |min_num(11) | 18.952|

sad_value7(0) |min_num(2) | 18.278|

sad_value7(0) |min_num(3) | 18.130|

sad_value7(0) |min_num(4) | 19.240|

sad_value7(0) |min_num(5) | 19.185|