# Multi-Level Programmable Array

20023179 Kim, Hyung ock

#### Inroduction

### □ Regular Structures

- Why? Easy to P&R( almost no need to P&R )

- Examples

- PLA like

- Binary Tree base

- Lattice Diagram

- Better solution than UAA

- UAA is treated as attempt to combine PLA-like and tree-like

#### Inroduction

- This Presentation is composed as following

- Intro to Lattice Diagram

- MOPS for multiple-out Lattice Diagram

- Generalized architecture for MOPS

## 1. Intro to Lattice Diagram

#### Chacteristics

- Like Tree and similar to BDD.

- BDD has combined predecessors if and only if predecessors in the same level is equal.

- But Lattice Diagram has always combine neighbor predecessors by some Rule. It occurs repetition of control variables.

- Although BDD grows horizontally, Lattice grows vertically by the repetition of variables...

- BDD and Lattice Diagram is made of MUX.

### 1. Intro to Lattice Diagram

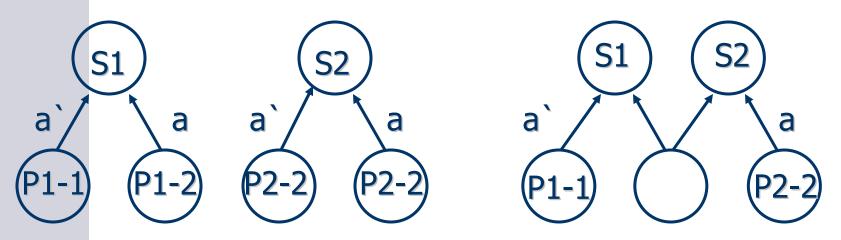

#### Combining Rule

Basic rule is the combining of two predecessors by XOR

(a AND P1-2) XOR (a' AND P2-1)

More rule and method are introduced in "LATTICE DIAGRAMS USING REED-MULLER LOGIC" by Perkowski

### Some problems in Lattice Diagram

- Repetition of control variable

- It increases vertical depth.

- This problem controlled by variable ordering.

- In the case of multi-output func

- Ordering is not easy to be performed

- There is quite waste for one block

- And Partitions generate big empty subareas

- Not good method, it leads to horizontal growth.

### □ Functional Decomposition

- Basic conception is to divide function to subfunctions

- There are some decomposition methods

- AND Decomposition, OR ~, Decomposition with Mux

- Multi-output func can be decomposed by symmetric func

- Multi-output func can be composed of Boolean operation(AND, OR, EXOR) of symmetric funcs.

- Because of no repetition of variable in symmetric func, this method is very nice to reduce vertical depth.

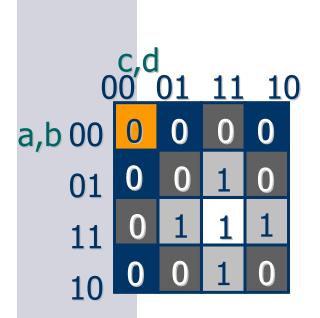

### ■ What is symmetric func?

- All minterms that have same number of ones in their binary number have same value( zero, or one ).

- Eg

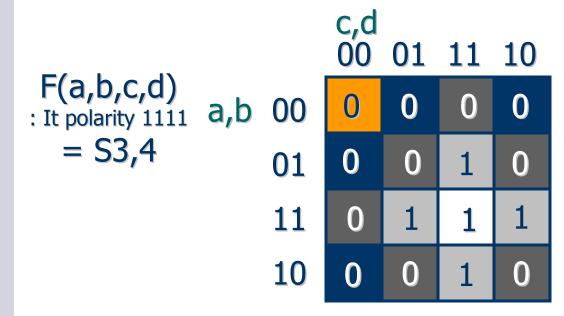

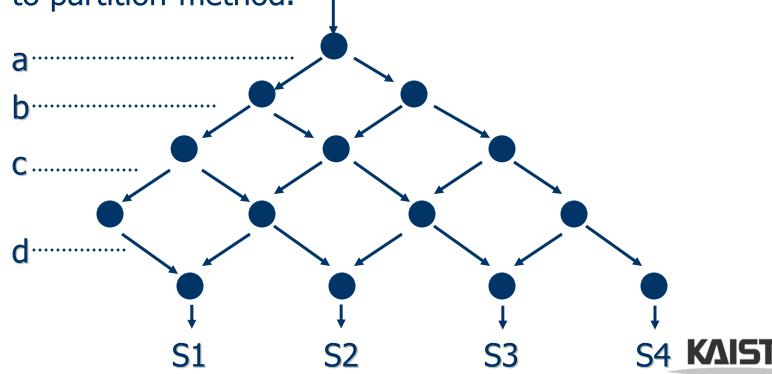

#### ■ MOPS for 4-variables

MOPS is one diagram but it can express all symmetric func which has same polarity

So that reason, it reduces horizontal width compare to partition-method.

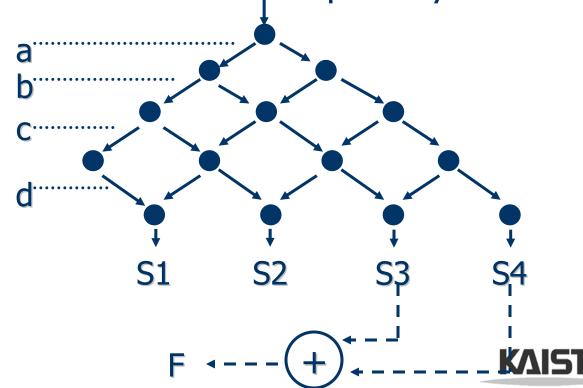

### ■ Examples of using MOPS

- $F = (\sim b \text{ XOR } \sim d) \text{ OR } (a \text{ XOR } c) \text{ OR } (abcd)$

- → It is decomposed to two symmetric functions S3, S4 that have same polarity

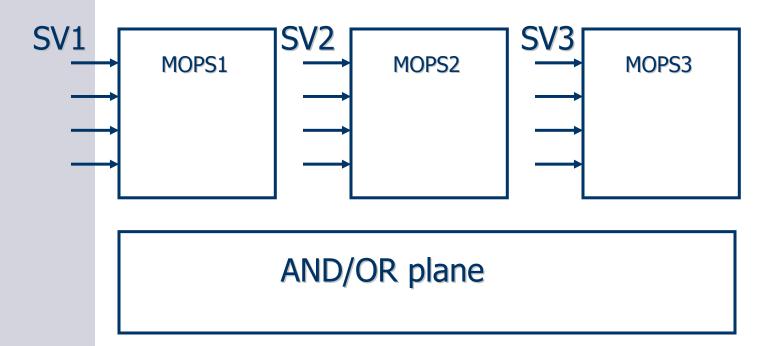

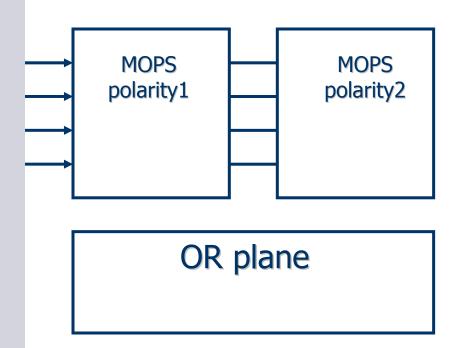

### 3. Generalized architecture for MOPS

- Every multi-output Boolean func can be decomposed to vector-OR of symmetric func of variable polarity

- Each MOPS has same control variable but different polarity

- Outputs of two MOPSes are combined in OR plane

### 3. Generalized architecture for MOPS

- Every multi-output func with subset SVi, i= 1~k of mutual symmetric variables can be decompsed to serial composition of K MOPS arrays followed by AND/OR plane.

- F(SV) = f1(SV1) OR f2(SV2) ... OR fk(SVk)

- Each fi(SVi) is symmetric, it can be expressed by one MOPS