### ECE - 590

# DIGITAL SYSTEM DESIGN USING HARDWARE DESCRIPTION LANGUAGE

## HOMEWORK - 1

## MEMORY CONTROLLER AND DATAPATH

GANKIDI VASU – 920361483, email: <u>vasu@pdx.edu</u> VISHWAS PULUGU – 935084168, email: <u>vishwas@pdx.edu</u>

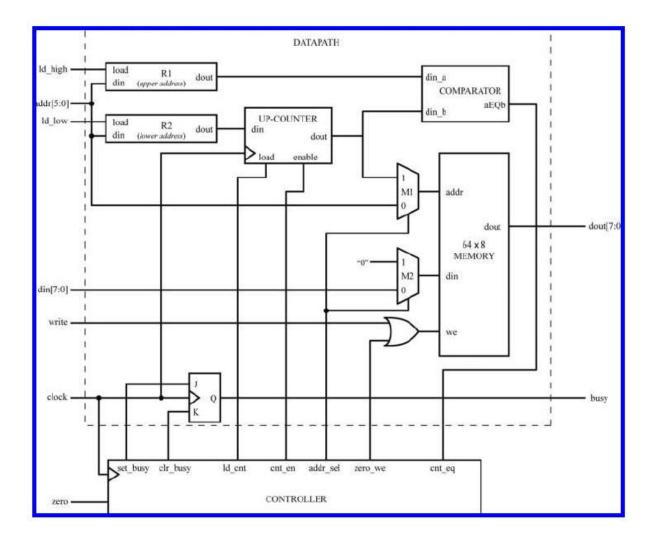

### Memory Controller and Datapath:

The controller for the datapath operates in two modes: "normal" and "zero". In normal mode memory performs write or read operation to specified address depending on the write signal. In zero mode system writes zeroes to all addresses in the range specified by registers R1 and R2. These registers are loaded in Normal mode. The system should assert busy in Zero mode.

### Datapath:

#### Inputs of the datapath:

ld\_high,ld\_low : 1 bit inputs to registers R1 and R2 according to which value in addr is loaded into one of the registers.

addr[5:0]: 6 bit input address for the memory.

din[7:0]: 8 bit data to be written into the memory.

Write: 1 bit signal which activates write process to the selected address.

Clock: synchronising signal for controller and datapath.

#### Ouputs of datapath:

aEQb: 1 bit signal indicating the completion of range of addresses between R1 and R2

dout[7:0] : gives the value of data in memory at given address.

Busy: signal indicating that the system is in zero mode and any inputs will be ignored.

#### Function of each block:

#### **Registers:**

It has two registers R1 and R2. R1 holds higher address and R2 holds lower address. Both the registers are loaded with value in addr[5:0] input depending on the values of Id\_high and Id\_low inputs. Both the registers have dout, which holds the address in that register as output. dout of R1 passes the address in R1 to comparator while dout of R2 passes the address in R2 to up counter module.

#### Up-Counter:

The functioning of Up-Counter is controlled by Id\_cnt and cnt\_en signals from controller. When Id\_cnt is asserted the address from R2 is loaded into the counter. When cnt\_en is asserted the up\_counter starts incrementing the address value and passes it to comparator each clock cycle.

#### Comparator:

It gets high address value from R1 and incremented address value from Up-Counter each clock cycle. Whenever both the values are equal, it asserts aEQb output signal.

#### Multiplexers:

there are two multiplexers M1 and M2. M1 multiplexes the input address to datapath and the address from up\_counter. One of these two is selected by the addr\_sel signal from the controller. M2 multiplexes input data to datapath and zero bits. It is also controlled by addr\_sel signal from controller. In zero mode addr\_sel value is 1 and it selects address from up-counter and data will be bits of 0. In normal mode addr\_sel value is 0 and Multiplexers select address, data from datapath input.

#### Memory:

Memory has addr, din and we as inputs and dout as output. When we is asserted, the value of din is written to the memory location pointed by addr and dout holds this data. If we is not asserted, dout displays the data at address location pointed by addr.

#### CONTROLLER:

Controller operates in two modes normal mode and zero mode. In normal mode the memory can perform a write operation to the specified address (if write is asserted). And in zero mode the system writes zeros to all address in the range specified by registers R1 and R2. These registers are loaded in normal mode. The system asserts busy when it's busy (in zero mode), and not respond to inputs during that time.

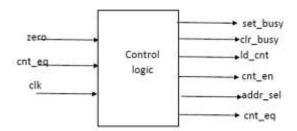

The controller in this digital module has four inputs and seven outputs. The input signals are clock, zero, reset, cnt\_eq. and the output signals are cnt\_en ,set\_busy ,clr\_busy ,ld\_cnt ,addr\_sel ,zero\_we. A single clock is used to both the controller and datapath.

#### Inputs:

**Zero** – The input zero is used to decide the mode of the controller, if zero = 1 then the controller is used to write zero's to the memory in the specified address range (loaded into the registers R1 and R2). if zero = 0 then the system is in normal mode in which the controller is used to write and read data to/from specified address.

Reset – reset's the controller to initial state. i.e. normal mode.

**Cnt\_eq** - if cnt\_eq = 1 this implies that the write operation has been completed in the zero mode and returns to the initial state.

#### Outputs:

**Cnt\_en** – is used to enable the up counter.

**Set\_busy** and **clr\_busy** – set\_busy is high and clr\_busy is low in the zero mode which makes the busy flag of the controller high, which indicates the inputs given to the controller in zero mode are not considered. Whereas the set\_busy is low and clr\_busy is hign in the normal mode which makes the busy flag go low, which indicates the registers can be loaded and data can be written and read from memory i.e. normal mode of operation.

Ld\_cnt – loads the value of the register R2 into the UPCOUNTER.

**Addr\_sel** – in the normal mode the value of Addr\_sel is set to 0 so that the data can be read/write from/to a memory location. In the zero mode the value of Addr\_sel is set to 1 so that the we can write zero's to the chunk of memory specified by the registers R1 and R2.

**Zero\_we** – is 0 in the normal mode which enables the memory to read and write the data based on the write signal value in the datapath.

Zero\_we is 1 in the zero mode which enables writing only zero's to the memory i.e. it doesn't support read operation in zero mode.

#### Finite State Machine: (Moore state machine)

There are three states in the FSM normal, load and zero.

State outputs:

OUTPUTS\STATES NORMAL\_STATE LOAD\_STATE WRITE\_STATE

| SET_BUSY | 0 | 1 | 1 |

|----------|---|---|---|

| CLR_BUSY | 1 | 0 | 0 |

| LD_CNT   | 0 | 1 | 0 |

| CNT_EN   | 0 | 0 | 1 |

| ADDR_SEL | 0 | 1 | 1 |

| ZERO_WE  | 0 | 1 | 1 |

**Normal** – until the value of the input zero is one the controller is in this state. In state the registers R1 and R2 are loaded and write and read from/to memory can be done. The outputs of the controller in this state are-

set\_busy <= '0'; clr\_busy<='1'; ld\_cnt<='0'; cnt\_en<='0'; addr\_sel<='0'; zero\_we<='0';</pre>

**load** – in this state the ld\_cnt is set to one, such that the upcounter is loaded to with the value of the value of the register R2 and the busy flag is set to 1. Such that the data is not written to the memory or read from memory in this state. The outputs of the controller in this state are-

set\_busy <='1'; clr\_busy<='0'; ld\_cnt<='1'; cnt\_en<='0'; addr\_sel<='0'; zero\_we<='0';</pre>

**Zero** – this state is immediately followed by load state without any input condition for the transition. In this state the zero\_we is one which is the input to multiplexer which enables writing zero to the range specified by registers R1 and R2. The outputs of the controller in this state are-

```

set_busy <= '1';

clr_busy<='0';

ld_cnt<='0';

cnt_en<='1';

addr_sel<='1';

zero_we<='1';</pre>

```

#### Testing:

Bothe the modes of system are verified. First R1 and R2 are loaded with high and low addresses. Then zero asserted. It resulted in system writing zeroes through the range of addresses between given input addresses.

|                   | 1.10 |        |          |     |          |                |                 |               |                 |          |

|-------------------|------|--------|----------|-----|----------|----------------|-----------------|---------------|-----------------|----------|

| Us clock          | 0    |        |          |     |          |                |                 |               |                 |          |

| 1 zero            | 0    |        |          |     |          |                |                 |               |                 |          |

| 14 reset          | 0    |        |          |     |          |                |                 |               |                 |          |

| 1. Id_tow         | 0    |        | 2        |     |          |                |                 |               |                 |          |

| 14 Id_high        | .0   |        |          |     |          |                |                 |               |                 |          |

| 12 write          | 0    |        |          |     |          |                |                 |               |                 |          |

| ▶ 📑 addr[5:0]     | oc   | 000000 | 000001   | (   |          | 000111         |                 |               | 001000          | 001011   |

| 🕨 📲 din(7:0)      | oc   | (      |          |     | 00000000 |                |                 | )             | ( 10 10 10 10 ) | 01010101 |

| dout[7:0]         | υτ   |        | UUUUUU   | UU  | (000)    | 0)(00000)(0000 | 10)(00000)(000¢ | 0)(00000)(000 | 0) 10101010     | 01010101 |

| busy              | υ    |        | 0.000000 |     |          |                |                 |               |                 |          |

| ▶ 🚮 addr_low(5:0) | υυ   |        | (        |     |          | 000            | 001             |               |                 |          |

| addr_high[5:0]    | στ   | 000    | ))))     | ć — |          |                | 000111          |               |                 |          |

| 1 clk_period      | 10   |        |          |     |          | 10000 ps       |                 |               |                 |          |

|                   |      |        |          |     |          |                |                 |               |                 |          |

|                   |      |        |          |     |          |                |                 |               |                 |          |

|                   |      |        |          |     |          |                |                 |               |                 |          |

For normal mode, zero is deasserted and different data was written to two different address locations by asserting write signal. Then by deasserting the write signal same addresses were given as input and the data read from these locations was as expected.

| U clock               | 1     |       |    |         |              |          |          |             |        |          |

|-----------------------|-------|-------|----|---------|--------------|----------|----------|-------------|--------|----------|

| The zero              | 0     |       |    |         |              |          |          |             |        |          |

| 1 reset               | 0     |       |    |         |              |          |          |             | -      |          |

| 1 Id_low              | 0     |       |    |         |              |          |          |             |        |          |

| 12 Id_high            | a     |       |    |         |              |          |          |             |        |          |

| 1 write               | 0     |       |    |         | THE MINISTER |          |          |             |        |          |

| ▶ 📲 addr(5:0)         | oc    | 0001  | 11 | ×       | 001000       | X 001    | p11      | 00 1000     | *      | 001011   |

| ▶ <b>■</b> ₩ din[7:0] | oc    | 00000 | 00 | x       | 10 10 10 10  | <u>ж</u> |          | 0101        | C 10 1 |          |

| ▶ 📑 dout[7:0]         | oc    | 000   | 0  | 00X0000 | 0            | X 0101   | 0101     | 10 10 10 10 | *      | 01010101 |

| Lie busy              | 1     |       |    |         |              |          |          |             |        |          |

| addr_low[5:0]         | 00    |       |    |         |              |          | 000001   |             |        |          |

| ▶ 📲 addr_high(5:      | D] OC |       |    |         |              |          | 0001111  |             |        |          |

| 1 clk_period          | 10    |       |    |         |              |          | 10000 ps |             |        |          |

|                       |       |       |    |         |              |          | -        |             |        |          |

|                       |       |       |    |         |              |          |          |             |        |          |