# VHDL-II Structural Modeling

#### ECE-331, Digital Design Prof. Hintz Electrical and Computer Engineering

#### Exist Only Within an Architecture

- Values of variables cannot be passed to other entities except through signals

- Variables Change Value When They Are Evaluated.

- Signals change at a "later" time

#### Entities are Interconnected by Signals

- Process executions result in new values being assigned to signals which are then accessible to other processes

- A signal <u>may be accessed</u> by a process in another architecture by connecting the signal to ports in the the entities associated with the two architectures

- Signals Can Be Declared Internal to an Architecture to Connect Internal Entities

Variables Are Not Appropriate Since They Do Not Have the Temporal Characteristics of Hardware

- Signals Declared Within an Entity <u>Are Not</u> <u>Available to Other Entities Unless Specified</u> <u>in the Port Clause</u> of the Entity Declaration.

Entity Syntax

entity identifier is

[ port ( port\_interface\_list ); ]

{ entity\_declarative\_item }

end [ entity ] [ identifier ] ;

#### Entity Syntax

port\_interface\_list <=</pre> ( identifier { , . . . } : [ mode ] subtype\_indication [ := expression ] ) { ; . . . } mode <= in out inout

#### Entity Example

#### Architecture Syntax

architecture identifier of

entity\_name **is**

{ block\_declarative\_item }

begin

{ concurrent\_statement }

end [architecture][ identifier ];

#### Structural Model

- A Representation of a System in Terms of the Interconnections of a Set of Defined Components.

- Components can be described either <u>structurally or behaviorally</u>

- Smallest components are behavioral entities

- Components usually stored in libraries

#### Structural Models

Components Can Be <u>Instantiated</u> As **Concurrent Statements in Architectures** – If architecture not specified in statement ■ Must be specified later, or Most recently analyzed architecture used - Ports can be specified two ways Positional association Named association

#### Structural Model Internal Signals

- Entity Ports Which are Declared within an Architecture Body Are Local Signals

- These signals are not available outside the architecture unless connected to one of the architecture's ports

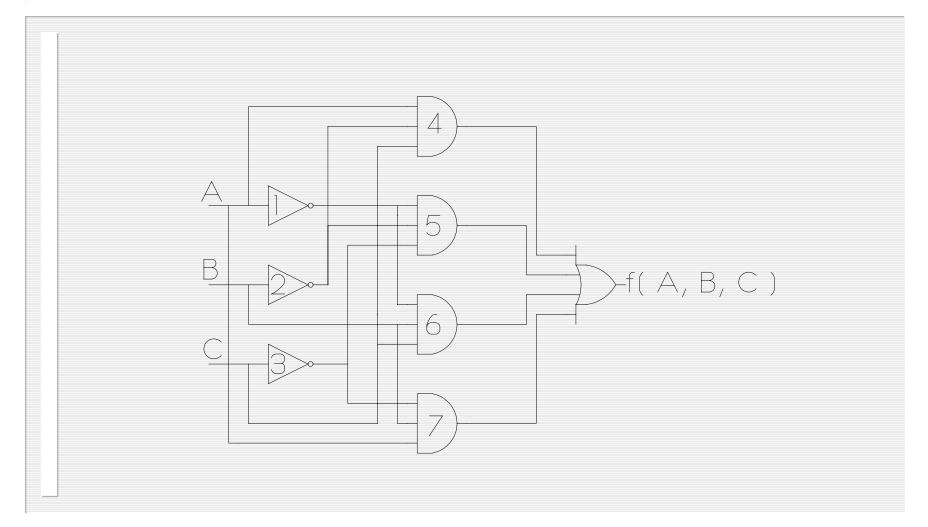

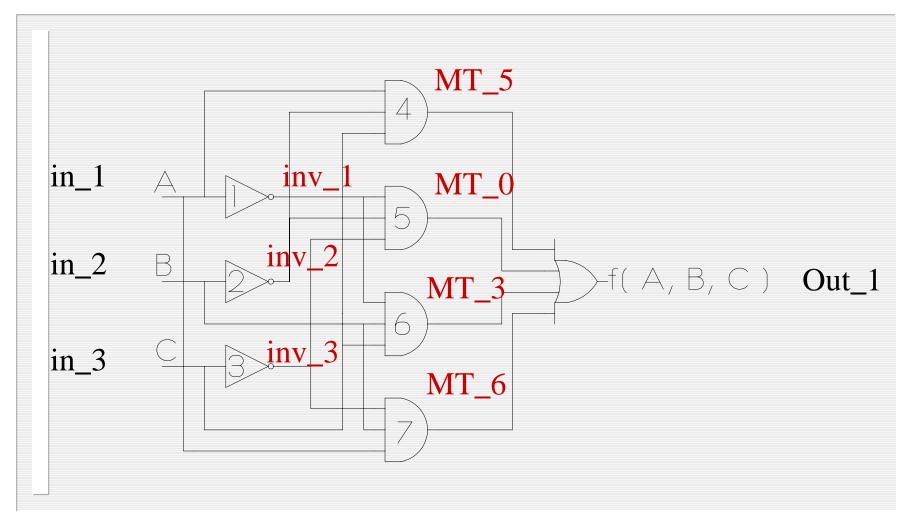

## Odd Parity Generator Example

## Parity Entity

entity Odd\_Parity is port( IN\_1, IN\_2, IN\_3 : in bit ; Out\_1 : out bit ); end entity Odd\_Parity ;

#### Odd Parity Behavior Architecture

**architecture** Odd\_Parity\_B **of** Odd\_Parity **is**

$f_{odd}(A,B,C) = A\overline{B}C + \overline{A}\overline{B}\overline{C} + \overline{A}BC + AB\overline{C}$

#### begin

Out\_1 <= ( IN\_1 and not IN\_2 and IN\_3 )

OR ( not IN\_1 and not IN\_2 and not IN\_3 )

OR ( not IN\_1 and IN\_2 and IN\_3 )

OR ( IN\_1 and IN\_2 and not IN\_3 )

end architecture Odd\_Parity\_B ;</pre>

#### INV Entity/Architecture

```

entity INV is

port(

In_1 : in bit ;

In_1_Bar : out bit );

end entity INV ;

architecture INV_B of INV is

begin

In_1_Bar <= not IN_1 ;</pre>

end architecture INV_B ;

```

### AND\_3 Entity/Architecture

```

entity AND_3 is

port(

IN_1, IN_2, IN_3 : in bit ;

Out 1

: out bit );

end entity AND 3 ;

architecture AND_3_B of AND_3 is

begin

Out_1 <= IN_1 and IN_2 and IN_3 ;

end architecture AND_3_B ;

```

# OR\_4 Entity/Architecture

```

entity OR 4 is

port(

IN_1, IN_2, IN_3, IN_4 : in bit ;

: out bit );

Out 1

end entity OR 4 ;

architecture OR_4_B of OR_4 is

begin

Out_1 <= IN_1 \text{ or } IN_2 \text{ or } IN_3 \text{ or } IN_4 ;

end architecture OR_4_B ;

```

#### Odd Parity Structural Arch.

```

architecture Odd_Parity_S of

Odd Parity is

--block_declarative_items

--components

component INV is

port(

In_1 : in bit ;

In_1_Bar : out bit );

end component INV ;

```

#### Odd Parity Structural Arch

component AND\_3 is port( IN\_1, IN\_2, IN\_3 : in bit ; : out bit ); Out 1 end component AND\_3 ; component OR\_4 is port( IN\_1, IN\_2, IN\_3, IN\_4 : in bit ; : out bit ); Out 1 end component OR\_4 ;

# Structural Mapping

#### Odd Parity Structural Arch

--block declarative items --internal signals signal MT\_0, MT\_3, MT\_5, MT\_6 : bit ; signal INV\_1, INV\_2, INV\_3 : bit ; **begin** --parity structural architecture --connect gates G1: INV port map ( In\_1, INV\_1 ); G2: INV port map ( In\_2, INV\_2 ); G3: INV port map ( In\_3, INV\_3 );

#### Odd Parity Structural Arch

```

G4: AND_3 port map

( IN_1, INV_2, IN_3, MT_5 );

G5: AND_3 port map

( INV_1, INV_2, INV_3, MT_0 );

G6: AND_3 port map

( INV_1, IN_2, IN_3, MT_3 );

G7: AND_3 port map

( IN_1, IN_2, INV_3, MT_6 );

```

#### Odd Parity Structural Arch.

G8: OR\_4 port map ( MT\_0, MT\_3, MT\_5, MT\_6, Out\_1 ); end architecture Odd\_Parity\_S ;

- Method for Grouping Related Declarations Which Serve a Common Purpose

- <u>Set of subprograms</u> to operate on particular data type

- <u>Set of declarations</u> for particular model

- Allows declaration of <u>"global" signals</u>, *e.g.*, clocks.

Design Unit Similar to Entity Declarations and Architecture Bodies

- Can be put in library and made accessible to other units

- Access to items declared in the package is through using its *Selected Name*

■ library name . package name . item name

Aliases can be used to allow shorter names for accessing declared items

#### Two Components to Packages

- Package declaration

- Package body

Not necessary if package declaration does not declare subprograms

# Package Declaration

#### Declares

- Subprograms using header, implementation is hidden

- Constants, do not need to be initialized in declaration

- Types, must be completely specified

- Can have variable size arrays

- Signals must be completely specified

# Package Declaration Syntax

package identifier is

{ package\_declarative\_item }

end [ package ] [ identifier ] ;

#### Package Declaration Examaple

package dp32\_types is

constant unit\_delay : Time := 1 ns;

type bool\_to\_bit\_table is array

(boolean) of bit;

end dp32\_types ;

## Package Body

Declared Subprograms Must Include the Full Declaration As Used in Package

Declaration

- Numeric literals can be written differently if same value

- Simple name may be replaced by a selected name provided it refers to same item

#### Package Body

May Contain Additional Declarations Which Are Local to the Package Body

Cannot declare signals in body

Package Body

package body identifier is

#### end [ package body ] [ identifier ] ;

#### End of Lecture