# On Universality of Ternary Reversible Logic Gates

Pawel Kerntopf\*, Marek A. Perkowski\*\*, Mozammel H. A. Khan\*\*\*

\*Institute of Computer Science, Department of Electronics and Information Technology, Warsaw University of Technology, Nowowiejska 15/19, 00-665 Warsaw, POLAND, <a href="mailto:pke@ii.pw.edu.pl">pke@ii.pw.edu.pl</a>

\*\*Department of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology (KAIST), 371-1 Gusong-dong, Yusong-gu, Daejeon 305-701, KOREA, <a href="mailto:mperkows@ee.kaist.ac.kr">mperkows@ee.kaist.ac.kr</a>

\*\*\*Department of Computer Science and Engineering, East West University, 45 Mohakhali, Dhaka 1212,

BANGLADESH, <a href="mailto:mhakhan@ewubd.edu">mhakhan@accesstel.net</a>

#### **Abstract**

A set of *p*-valued logic gates (primitives) is called universal if an arbitrary *p*-valued logic function can be realized by a logic circuit built up from a finite number of gates belonging to this set. In the paper, we consider the problem of determining the number of universal ternary reversible logic gates with two inputs and two outputs. We have established that over 97% of such gates are universal. Some of the theoretical results are also valid for arbitrary *p*-valued reversible logic gates.

#### 1. Introduction

The *universality* (or completeness) of sets of binary and multiple-valued functions and related problems have been studied for many years and by many researchers in three areas: propositional calculus of logics, universal algebras and logic (switching) circuits ([49] contains 464 references). The universality of logic gates (primitives) depends on the technology because it has to take into account also some constraints. It may differ from the notion of functional completeness studied by mathematicians and for this reason sometimes is called elemental universality [19]. This area has been gradually evolving. Initially, it dealt with delay-less combinational circuits exclusively [37]. Later, delays have also been taken into account as well as universality of sequential primitives was considered (including asynchronous behavior) [19, 40]. With technological changes new types of universality have been developed, e.g. corresponding to double-rail signals [21].

Although studies of reversible computing were initiated in the 1960s [31, 6] and a number of universal reversible logic gates have been proposed, general problems of universality of such gates have attracted the attention of researchers only very recently. Few papers have been devoted so far to universality of reversible gates and they consider almost exclusively binary gates [52, 14, 26]. In this paper, we are concerned entirely with universality of general ternary reversible gates.

A gate (or a circuit) is called *reversible* if there is a one-to-one correspondence between its input and output assignments, i.e. not only the outputs can be uniquely determined from the inputs, but also the inputs can be recovered from the outputs. In other words, a gate is reversible if it is invertible or information-lossless. Using reversible logic circuits enables avoiding energy losses in digital devices [31, 18, 6, 10, 11, 17]. It is a fast developing area of research due to its increasing importance to future computer technologies, especially quantum ones [16] because of possibility to solve some exponentially hard problems in polynomial time [7]. For example, during the last three years many papers have been written on reversible computing [1-5, 8, 12-15, 20, 22-26, 28-30, 32-36, 41-48, 51, 54, 55], some of them proposing new multiple-valued gates [48, 42, 5, 14, 1-3, 41, 44, 30]. In designing circuits built from such gates it is important to know which of the gates have the least cost. Solving this practical problem we should first establish how many multiple-valued gates are universal.

Let us call a gate with n inputs and m outputs an n\*m-gate. Some of the binary reversible gates considered in the literature have different number of inputs and outputs, e.g. 2\*3 "switch gate" and 2\*4 "interaction gate" [18] (also called  $I_B$  and  $II_B$  elements, respectively, in [27, 50]). However, usually it is assumed that a reversible gate has the same number of inputs and outputs. In this case, the output rows of the truth table of a reversible gate can be obtained by permutation of the input rows. Thus, there are equal numbers of all values in the function vector for each output function of a reversible gate (such functions are called *balanced* [9]).

Universality of reversible gates differs from classical elemental universality because in reversible circuits

- (1) usually multi-output gates are considered instead of only one-output gates,

- (2) a constant signal may be applied to an arbitrary number of inputs,

- (3) reversible gates have fan-out of each output equal to 1.

Thus we have to consider

- (1) universality of sets of functions instead of single functions,

- (2) weak completeness instead of strong completeness,

- (3) the property of replicating input signals at the gate outputs.

Compositional properties of binary and ternary reversible gates are different. Universal binary reversible k\*k gates exist only for  $k \ge 3$  [53] (the set of 2-variable balanced Boolean functions is equal to {EXCLUSIVE-OR, EQUIVALENCE} and it is known that this set is not weak complete). Over 97% of binary reversible 3\*3 gates and almost all reversible 4\*4 gates are universal [26] in spite of the reversibility constraint. However, there exist ternary 2\*2 gates that are universal. Moreover, the number of ternary reversible 2\*2 gates is 9 times greater than the number of binary reversible 3\*3 gates (9! in comparison with 8!). In binary case, for establishing universality of a gate it is sufficient to check weak completeness of the set of the gate output functions as it has been proved in [26] that all gates with this property are duplicating input signals. This result does not hold for ternary reversible gates. For this reason we have introduced a new property of gates called quasi-replicating. Using this notion it was possible to obtain experimental results allowing estimation of the number of universal ternary reversible 2\*2 gates. Namely, also over 97% of such gates are universal.

The rest of the paper is organized as follows. In Section 2, we define basic notions of reversible gates. Section 3 introduces the notion of universality of reversible gates (called *r-universality*, in short). Section 4 presents results of counting the number of r-universal ternary reversible 2\*2 gates. Finally, in Section 5, conclusions are made.

## 2. Preliminaries

Let  $P = \{0,1, ..., p-1\}$ . A mapping  $f: P^n \to P$  will be called an *n*-variable *p*-valued function. If p=3 then the function f is called *ternary*. To represent a 1-variable ternary function f(x) we use the vector of the function values written as a string  $a_0$   $a_1$   $a_2$ , where  $a_i = f(i)$ . For example, the identity function f(x) = x is represented by the vector 012. Similarly, to represent a 2-variable ternary function  $f(x_1,x_2)$  the vector  $a_0$   $a_1$   $a_2$   $a_3$   $a_4$   $a_5$   $a_6$   $a_7$   $a_8$  will be used, where  $f(j,k) = a_{3j+k}$ . For example, the function  $f(x_1,x_2) = x_1 + x_2 \pmod{3}$  will be represented by the vector 012120201.

#### **Definition 1** A set of *p*-valued functions *F* is

- complete (strong complete, Sheffer) if an arbitrary p-valued function  $f(x_1,...,x_n)$  can be realized by a loop-free combinational circuit built up of logic gates realizing functions from F and using  $x_1, ..., x_n$  as primary inputs,

- weak complete (complete with constants, pseudo-Sheffer) if an arbitrary p-valued function  $f(x_1,...,x_n)$  can be realized by a loop-free combinational circuit built up of logic gates realizing functions from F and using  $0, 1, ..., p-1, x_1, ..., x_n$  as primary inputs.

**Definition 2** Let  $w_i(f)$  denotes the number of input assignments X for which f(X) = i. An n-variable p-valued function f is called *balanced* if  $w_i(f) = p^{n-1}$  for each i, i.e. f is equal to each value belonging to the set  $\{0,1,\ldots,p-1\}$  the same number of times.

There are six 1-variable balanced ternary functions. They are represented by the vectors 012, 021, 102, 120, 201, 210 and corresponds to S<sub>3</sub>, the symmetric group on three marks. The function  $f(x_1,x_2) = x_1+x_2 \pmod{3}$  is one of 1,680 2-variable balanced ternary functions.

**Definition 3** A *p*-valued gate (or a circuit) is *reversible* if there is a one-to-one correspondence between the input and the output assignments, i.e. if in the truth table of the gate or circuit there is a distinct output row for each input row.

Note that every output function of a reversible gate is balanced and that the reversibility property of gates is preserved under permutations of inputs and/or outputs. We will consider only the gates with the same number of inputs and outputs. A gate with k inputs and k outputs will be called a k\*k-gate. There exist six ternary reversible 1\*1 gates (they have the same truth tables as 1-variable balanced ternary functions). As mentioned earlier only 1,680 out of  $3^9$ =19,683 2-variable ternary functions are balanced. The number of pairs of balanced ternary functions is equal to 1,680 $^2$  = 2,822,400. However, the number of ternary reversible 2\*2 gates is smaller: 9! = 362,880 (it is equal to the number of permutations of 9 rows in the truth table of a ternary reversible 2\*2 gate) as not every pair of balanced functions may appear in a ternary reversible 2\*2-gate (see Example 1).

**Definition 4** Two balanced *p*-valued functions *f*, *g* are called *r*-compatible if for all input assignments  $(a_1, ..., a_n)$  the pairs of their values  $\langle f(a_1, ..., a_n), g(a_1, ..., a_n) \rangle$  are equal the same number of times to each of the pairs  $\langle j, k \rangle$ ,  $0 \leq j, k \leq p-1$ .

**Example 1** Let the capital letters A, B denote inputs, and P, Q denote outputs of a ternary reversible 2\*2 gate. Table 1 shows an example of a pair of balanced functions that is not r-compatible. Namely, in the output rows of Table 1 each of the pairs <0,0>, <1,2> and <2,1> appears twice, while the combinations <0,2>, <1,1> and <2,0> are missing.

**TABLE 1**PAIR OF TERNARY BALANCED FUNCTIONS THAT IS NOT r-COMPATIBLE

| A B | P Q |

|-----|-----|

| 0 0 | 0 0 |

| 0 1 | 1 2 |

| 0 2 | 1 0 |

| 1 0 | 0 1 |

| 1 1 | 1 2 |

| 1 2 | 0 0 |

| 2 0 | 2 1 |

| 2 1 | 2 1 |

| 2 2 | 2 2 |

**Lemma 1** Each pair of functions belonging to the set of output functions of a *p*-valued reversible gate is *r*-compatible.

**Proof.** All  $p^n$  output rows in the truth table of a reversible n\*n gate are distinct. Thus for each pair of output functions f, g all pairs of values of these functions  $f(a_1,...,a_n)$ ,  $g(a_1,...,a_n)$  appear in the output part of the gate the same number of times. Hence the pair f, g is f-compatible.

**Lemma 2** All output functions of every *p*-valued reversible gate are distinct.

**Proof.** Let us assume that there exists a p-valued reversible gate with two identical output functions. In a pair of identical output columns only the following pairs of values appear: <0,0>, <1,1>, ..., <p-1,p-1>. Such a pair of functions is not r-compatible. By Lemma 1 we obtain a contradiction. Hence, Lemma 2 holds.

### 3. Universality of ternary reversible 2\*2 gates

**Definition 5** A *p*-valued reversible n\*n gate (or circuit) has *duplicating property* (*D-property*, in short) if there exist a sequence of n-1 constants  $a_1, \ldots, a_{i-1}, a_{i+1}, \ldots, a_n$  and two output functions of the gate (circuit)  $f_i(x_1, x_2, \ldots, x_n)$  and  $f_k(x_1, x_2, \ldots, x_n)$  such that

$$f_j(a_1,...,a_{i-1},x_i,a_{i+1},...,a_n) = f_k(a_1,...,a_{i-1},x_i,a_{i+1},...,a_n) = x_i.$$

**Example 2** Table 2 shows the truth table of a ternary reversible 2\*2 gate (circuit) having D-property. It is easy to notice that for A = 0 we always obtain the same value at both gate outputs P and Q as at the input B:

$$P = B$$

$Q = B$ .

TABLE 2

TERNARY REVERSIBLE 2\*2 GATE HAVING D-PROPERTY

| A     | В | P | Q   |

|-------|---|---|-----|

| 0     | 0 | 0 | 0   |

| 0     | 1 | 1 | 1   |

| 0     | 2 | 2 | 2   |

| 1     | 0 | 0 | 1   |

| 1     | 1 | 1 | 2 2 |

| 1     | 2 | 0 | 2   |

| 2     | 0 | 2 | 1   |

| 2 2 2 | 1 | 1 | 0   |

| 2     | 2 | 2 | 0   |

**Definition 6** A *p*-valued reversible n\*n gate (or circuit) has *quasi-duplicating property* (*qD-property*, in short) if it is has not D-property and there exist a sequence of n-1 constants  $a_1, \ldots, a_{i-1}, a_{i+1}, \ldots, a_n$  and two output functions of this gate  $f_j(x_1, x_2, \ldots, x_n)$  and  $f_k(x_1, x_2, \ldots, x_n)$  such that each of the functions

functions

$$f_j(a_1,\ldots,a_{i-1},x_i,a_{i+1},\ldots,a_n) \quad \text{ and } \quad f_k(a_1,\ldots,a_{i-1},x_i,a_{i+1},\ldots,a_n)$$

takes all values  $0,1,\ldots,p$ -1.

**Example 3** Table 3 shows the truth table of a ternary reversible 2\*2 gate (circuit) having qD-property. It is easy to notice that for B = 0 the output functions P and Q have the representations 012 and 201, respectively.

**TABLE 3**TERNARY REVERSIBLE 2\*2 GATE HAVING qD-PROPERTY

| A   | В | P | Q |

|-----|---|---|---|

| 0   | 0 | 0 | 2 |

| 0   | 1 | 0 | 0 |

| 0   | 2 | 0 | 1 |

| 1   | 0 | 1 | 0 |

| 1   | 1 | 1 | 1 |

| 1   | 2 | 2 | 0 |

| 2   | 0 | 2 | 1 |

| 2 2 | 1 | 1 | 2 |

| 2   | 2 | 2 | 2 |

**Theorem 1** If G is a p-valued reversible n\*n gate with qD-property then a circuit with D-property can be built using exclusively gates G.

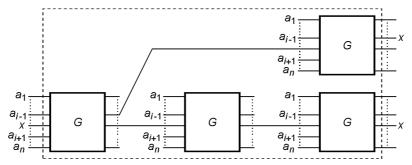

**Proof** Let us consider ternary case. If f is a 1-variable ternary function and  $f^2(x) = f(f(x))$ ,  $f^3(x) = f(f^2(x))$  then  $f^2 = f$  for f belonging to  $A_1 = \{021, 102, 210\}$ , and  $f^3 = f$  for f belonging to  $A_2 = \{120, 201\}$ . Assume that a ternary reversible n\*n gate G has qD-property. Then there exists a sequence of n-1 constants  $a_1, \ldots, a_{i-1}, a_{i+1}, \ldots, a_n$  and two output functions of this gate  $f_j(x_1, x_2, \ldots, x_n)$  and  $f_k(x_1, x_2, \ldots, x_n)$  such that each of the functions  $f_j(a_1, \ldots, a_{i-1}, x_b, a_{i+1}, \ldots, a_n)$  and  $f_k(a_1, \ldots, a_{i-1}, x_b, a_{i+1}, \ldots, a_n)$  takes all three values 0,1,2. First, we will consider an example. Let the representation of  $f_j(a_1, \ldots, a_{i-1}, x_b, a_{i+1}, \ldots, a_n)$  belongs to  $A_1$  and the representation of  $f_k(a_1, \ldots, a_{i-1}, x_b, a_{i+1}, \ldots, a_n)$  belongs to  $A_2$ . Fig. 1 shows a circuit with D-property built using exclusively gates G. In general, if the representation of the function  $f_m(a_1, \ldots, a_{i-1}, x_b, a_{i+1}, \ldots, a_n)$ , where m = j or k, belongs to  $A_1$  ( $A_2$ ) then we construct a sequence of two (three) gates in which the j-th output of the first gate is connected to the i-th input of the second and third gate, respectively). When the first gate is common for the two sequences then the signal at the j-th output of one sequence and the signal at the k-th output of the other sequence are both equal to the i-th input of the common gate. Thus Theorem 1 holds in ternary case. The proof for p-valued case is similar (based on properties of permutation groups). We are not including it due to the lack of space.

Fig. 1 Example of a circuit with D-property built using gates G with qD-property

It is possible to build up a circuit with qD-property (and by Theorem 1 also a circuit with D-property) using gates not having qD-property as shown in the example below.

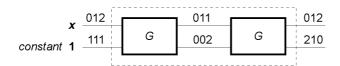

**Example 4** Table 4 shows the truth table of a ternary reversible 2\*2 gate not having qD-property. Fig. 2 presents a circuit with qD-property built using such gates. Thus it is also possible to build up a circuit with D-property using circuits from Fig. 2.

**TABLE 4**TERNARY REVERSIBLE 2\*2 GATE NOT HAVING qD-PROPERTY

| A | В | P | Q |

|---|---|---|---|

| 0 | 0 | 0 | 2 |

| 0 | 1 | 0 | 0 |

| 0 | 2 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 |

| 1 | 2 | 2 | 0 |

| 2 | 0 | 2 | 1 |

| 2 | 1 | 1 | 2 |

| 2 | 2 | 2 | 2 |

Fig. 2 Circuit with qD-property built up using gate G not having qD-property

**Definition 7** A *p*-valued reversible gate *G* is *r*-universal if an arbitrary *p*-valued function  $f(x_1,...,x_n)$  can be realized by a loop-free combinational circuit built up of a finite number of copies of the gate *G* using constants an arbitrary number of times and using each signal  $x_1, ..., x_n$  at most once as primary inputs.

**Theorem 2** If for a p-valued reversible gate G it is possible to built a circuit having qD-property using gates G and the set of output functions of G is weak complete then G is r-universal.

**Proof.** Proofs of universality in classical case (see e.g. [37]) are based on the assumption that each input signal may be used an arbitrary number of times (i.e., arbitrary number of copies of primary inputs can be used). Then from a canonical form of a function it follows that a circuit realizing any function can be built. Thus it is sufficient to follow these arguments to prove Theorem 2. As it is possible to built a circuit having qD-property using gates G then by Theorem 1 it is possible to build a circuit with D-property using gates G. However, this is equivalent to the assumption that each signal may be used any number of times. Hence, Theorem 2 holds.

# 4. Experimental results

First we have run a program based on the procedure from [39] to find all ternary reversible 2\*2 gates that are weak complete. Then for each such gate we have constructed cascade circuits (allowing wire crossing) to check whether conditions of Theorem 2 have been fulfilled. Because the number of these cascade circuits grows exponentially with the number of levels we have limited the calculations to 12 levels.

On the basis of Theorem 2 we were able to establish that among 362,880 ternary reversible 2\*2 gates:

- a) 353,214 (97.34%) are r-universal,

- b) 1,934 (0,53%) are not weak complete, thus are not r-universal,

- c) 7,732 (2.13%) are weak complete, but it is not known whether they are r-universal (circuits with qD-property built up of gates G have not been found).

# 5. Conclusions

By exhaustive calculations we have established that over 97% of all ternary reversible 2\*2 gates are r-universal. As there are so many universal gates the circuit designers have a lot of freedom in finding gates with good physical implementations (e.g. minimum cost). Some such multivalued gates have been proposed for quantum logic [38] and generalized in [41, 44, 30]. However, nobody has done such research for CMOS, DNA and nanotechnologies where a number of binary gates have been proposed.

Theorem 2 gives a sufficient condition for r-universality. However, we do not know whether it is also a necessary condition. It is an interesting open problem.

## 6. References

- [1] A. Al-Rabadi, Novel Methods for Reversible Logic Synthesis and Their Application to Quantum Computing, Ph,D, Thesis, Portland State University, Portland, Oregon, Oct. 2002.

- [2] A. Al-Rabadi, "Reversible Logic Synthesis Using Iterative Symmetry Indices Decomposition", *Proc.* 6<sup>th</sup> *Int'l Symp. on Representations and Methodology of Future Computing Technology*, 2003, pp. 104-112.

- [3] A. Al-Rabadi, "New Multiple-Valued Galois Field Sum-of-Product Cascades and Lattices for Multiple-Valued Quantum Logic Synthesis", *Proc.* 6<sup>th</sup> *Int'l Symp. on Representations and Methodology of Future Computing Technology*, 2003, pp. 171-182.

- [4] A. Al-Rabadi, L.W. Casperson, "Optical Realizations of Reversible Logic", *Proc.* 11<sup>th</sup> IEEE/ACM Int'l Workshop on Logic and Synthesis, 2002, pp. 21-26.

- [5] A. Al-Rabadi, M.Perkowski, "New Classes of Multi-Valued Reversible Decompositions for Three-Dimensional Layout", *Proc.* 5<sup>th</sup> Int'l Workshop on Applications of Reed-Muller Expansion in Circuit Design, 2001, p. 185-204.

- [6] C.H. Bennett, "Notes on the History of Reversible Computation", IBM J. Res. Dev., 1988, pp. 16-23.

- [7] C.H. Bennett, D.P. DiVincenzo, "Quantum Information and Computation", *Nature*, Vol. 404, 2000, pp. 247.

- [8] J.W. Bruce, M.A. Thornton, L. Shivakumaraiah, P.S. Kokate, X. Li, "Efficient Adder Circuits Based on a Conservative Reversible Logic Gate", *Proc. IEEE Symposium on VLSI*, 2002, pp. 83-88.

- [9] K. Chakrabarty, J.P. Hayes "Balanced Boolean Functions", *IEE Proceedings Computers and Digital Techniques*, Vol. 145, 1998, pp. 52-62.

- [10] A. De Vos, "Towards Reversible Digital Computers", *Proc. European Conf. on Circuit Theory and Design*, 1997, Vol. 2, pp. 923-931.

- [11] A. De Vos, "Reversible Computing", Progress in Quantum Electronics, Vol. 23, 1999, pp. 1-49.

- [12] A. De Vos, B. Desoete, A. Adamski, P. Pietrzak, M. Sibiński, T. Widerski, "Design of Reversible Logic Circuits by Means of Control Gates", *Integrated Circuit Design*, Lecture Notes in Computer Science, Vol. 1918, 2000, pp. 255-264.

- [13] A. De Vos, B. Desoete, F. Janiak, A. Nogawski, "Control Gates for Reversible Computers", *Proc.* 11<sup>th</sup> Int'l. Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS), 2001, pp. 9.2.1-9.2.10.

- [14] A. De Vos, B. Raa, L. Storme, "Generating the Group of Reversible Logic Gates", *Journal of Physics A: Mathematical & General*, Vol. 35, 2002, pp. 7063-7078.

- [15] G. Dueck, D. Maslov, "Reversible Function Synthesis with Minimum Garbage Outputs", *Proc.* 6<sup>th</sup> *Int'l Symp. on Representations and Methodology of Future Computing Technology*, 2003, pp. 154-161

- [16] R.Feynman, "Quantum Mechanical Computers", Optics News, Vol. 11, 1985, pp. 11-20.

- [17] M.P. Frank, Reversibility for Efficient Computing, Ph.D. Thesis, MIT, Cambridge, MA, 1999.

- [18] E. Fredkin, T. Toffoli, "Conservative Logic", Int'l J. of Theor. Physics, 1982, pp. 219-253.

- [19] K. Inagaki, "Elemental Universality of Sets of Logic Devices", *IEICE Trans. on Inf. & Syst.*, Vol. E81-D, 1998, pp. 767-772.

- [20] K. Iwama, Y. Kambayashi, S. Yamashita, "Transformation Rules for Designing CNOT-based Quantum Circuits", *Proc. Design Automation Conf.*, 2002, pp. 419-425.

- [21] S. Karunanithi, A.D. Friedman, "Some New Types of Logical Completeness", *IEEE Trans. on Computers*, Vol. 27, 1978, pp. 998-1005.

- [22] A. Khlopotine, M. Perkowski, P. Kerntopf, "Reversible Logic Synthesis by Gate Composition", *Proc.* 11<sup>th</sup> IEEE/ACM Int'l Workshop on Logic and Synthesis, 2002, pp. 261-266.

- [23] P. Kerntopf, "A Comparison of Logical Efficiency of Reversible and Conventional Gates", *Proc.* 9<sup>th</sup> IEEE Int'l Workshop on Logic Synthesis, 2000, pp. 261-269.

- [24] P. Kerntopf, "On Efficiency of Reversible Logic (3,3)-Gates", Proc. 7<sup>th</sup> Int'l Conf. On Mixed Design of Integrated Circuits and Systems, 2000, pp. 185-190.

- [25] P. Kerntopf, "Synthesis of Multipurpose Reversible Logic Gates", *Proc. EUROMICRO Symp. on Digital Systems Design*, 2002, pp. 259-266.

- [26] P. Kerntopf, "On Universality of Binary Reversible Logic Gates", *Proc.* 5<sup>th</sup> Int'l Workshop on Boolean Problems, 2002, pp. 47-52.

- [27] K. Kinoshita, T. Sasao, J. Matsuda, "On Magnetic Bubble Logic Circuits", *IEEE Trans. on Computers*, Vol. 25, 1976, pp. 247-253.

- [28] M.H.A. Khan, M.A. Perkowski, "Logic Synthesis with Cascades of New Reversible Gate Families", *Proc.* 6<sup>th</sup> *Int'l Symp. on Representations and Methodology of Future Computing Technology*, 2003, pp. 43-55.

- [29] M.H.A. Khan, M.A. Perkowski, "Multi-Output ESOP Synthesis with Cascades of New Reversible Gate Family", *Proc.* 6<sup>th</sup> *Int'l Symp. on Representations and Methodology of Future Computing Technology*, 2003, pp. 144-153.

- [30] M.H.A. Khan, M.A. Perkowski, P. Kerntopf, "Multi-Output Galois Field Sum of Product (GFSOP) Synthesis with New Quantum Cascades", *Proc.* 33<sup>rd</sup> IEEE Int'l Symposium on Multiple-Valued Logic, 2003.

- [31] R. Landauer, "Irreversibility and Heat Generation in the Computing Process", *IBM J. Res. Develop.*, Vol. 3, 1961, pp. 183-191.

- [32] M. Lukac, M. Pivtoraiko, A. Mishchenko, M. Perkowski, "Automated Synthesis of Generalized Reversible Cascades using Genetic Algorithms", *Proc.* 5<sup>th</sup> Int'l Workshop on Boolean Problems, 2002, pp. 33-45.

- [33] D. Maslov, G. Dueck, "Garbage in Reversible Designs of Multiple Output Functions", *Proc.* 6<sup>th</sup> *Int'l Symp. on Representations and Methodology of Future Computing Technology*, 2003, pp.162-170.

- [34] D.M. Miller, "Spectral and Two-place Decomposition Techniques in Reversible Logic", *Proc. Midwest Symposium on Circuits and Systems*, 2002.

- [35] D.M. Miller, G. Dueck, "Spectral Techniques for Reversible Logic Synthesis", *Proc.* 6<sup>th</sup> Int'l Symp. on Representations and Methodology of Future Computing Technology, 2003, pp. 56-62.

- [36] A. Mishchenko, M. Perkowski, "Logic Synthesis of Reversible Wave Cascades", *Proc.* 11<sup>th</sup> IEEE/ACM Int'l Workshop on Logic and Synthesis, 2002, pp. 197-202.

- [37] A. Mukhopadhyay, "Complete Sets of Logic Primitives", in *Recent Developments in Switching Theory* (edited by A. Mukhopadhyay), Academic Press, London 1971, pp. 1-26.

- [38] A. Muthukrishnan, C.R. Stroud Jr., "Multivalued logic gates for quantum computation", *Physical Review A*, vol.62, 2000, pp.052309.1-8.

- [39] J.C. Muzio, "Ternary Two-Place Functions that are Complete with Constants", *Proc.* 5<sup>th</sup> Int'l Symposium on Multiple-Valued Logic, 1975, pp. 27-33.

- [40] A. Nozaki, "Complete Sets of Switching Elements and Related Topics", *Proc.* 1<sup>st</sup> USA-JAPAN Computer Conf., 1972, pp. 12.5.1-4.

- [41] M.Perkowski, A. Al.-Rabadi, P. Kerntopf, "Multiple-Valued Quantum Logic Synthesis", *Proc. Int'l Symp. on New Paradigms VLSI Computing*, Sendai, Japan, 2002, pp.41-47.

- [42] M.Perkowski, A. Al.-Rabadi, P. Kerntopf, A. Mishchenko, M. Chrzanowska-Jeske, "Three-Dimensional Realization of Multi-Valued Functions using Reversible Logic", *Proc.* 10<sup>th</sup> Int'l Workshop on Post-Binary Ultra-Large-Scale Integration Systems, 2001, pp. 47-53.

- [43] M.Perkowski, L. Jozwiak, P. Kerntopf, A. Mishchenko, A. Al.-Rabadi, A. Coppola, A. Buller, Xiaoyu Song, Md. Mozammel Huq Azad Khan, S.N. Yanushkevich, V.P. Shmerko, Chrzanowska-Jeske, "A General Decomposition for Reversible Logic", *Proc.* 5<sup>th</sup> Int'l Workshop on Applications of Reed-Muller Expansion in Circuit Design, 2001, p. 119-138.

- [44] M.Perkowski, P. Kerntopf, A. Al.-Rabadi, M.H.A. Khan, "Multiple-Valued Quantum Computing. Issues, Open Problems, Solutions", *Technical Report*, KAIST, December 2002.

- [45] M.Perkowski, P. Kerntopf, A. Buller, M. Chrzanowska-Jeske, A. Mishchenko, X. Song, A. Al-Rabadi, L. Jozwiak, A. Coppola, B. Massey, "Regularity and Symmetry as a Base for Efficient Realization of Reversible Logic Circuits", *Proc.* 10<sup>th</sup> IEEE Int'l Workshop on Logic and Synthesis, 2001, pp. 90-95.

- [46] M.Perkowski, P. Kerntopf, A. Buller, M. Chrzanowska-Jeske, A. Mishchenko, X. Song, A. Al.-Rabadi, L. Jozwiak, A. Coppola, B. Massey, "Regular Realization of Symmetric Functions Using Reversible Logic", *Proc. EUROMICRO Symposium on Digital Systems Design*, 2001, pp. 245-252.

- [47] M. Perkowski, M. Lukac, M. Pivtoraiko, P. Kerntopf, M. Folgheraiter, D. Lee, H. Kim, W. Hwangbo, J.-W. Kim, Y.W. Choi, "A Hierarchical Approach to Computer-Aided Design of Quantum Circuits", *Proc.* 6<sup>th</sup> *Int'l Symp. on Representations and Methodology of Future Computing Technology*, 2003, pp. 201-209.

- [48] P. Picton, "A Universal Architecture for Multiple-Valued Reversible Logic", *Multiple-Valued Logic Journal*, Vol. 5, 2000, pp. 27-37.

- [49] I.G.Rosenberg, "Completeness Properties of Multiple-Valued Logic Algebras", in *Computer Science and Multiple-Valued Logic. Theory and Applications* (edited by D.C. Rine), North-Holland Publishing Company, Amsterdam-New York-Oxford 1977, pp. 144-186.

- [50] T. Sasao, K. Kinoshita, "Conservative Logic Elements and Their Universality", *IEEE Trans. on Computers*, Vol. 28, 1979, pp. 682-685.

- [51] V.V. Shende, A.K. Prasad, I.L. Markov, J.P. Hayes, "Reversible Logic Circuit Synthesis", *Proc. Int'l Conf. on Computer-Aided Design*, 2002.

- [52] L. Storme, A. De Vos, G. Jacobs, "Group Theoretical Aspects of Reversible Logic Gates", *Journal of Universal Computer Science*, Vol. 5, 1999, pp. 307-321.

- [53] T. Toffoli, "Reversible Computing", in *Automata*, *Languages and Programming*, edited by J.W. de Bakker and J. van Leeuwen, Springer Verlag 1980, pp. 632-644.

- [54] G. Yang, W.N.N. Hung, X. Song, M. Perkowski, "Majority-Based Reversible Logic Gate", *Proc.* 6<sup>th</sup> Int'l Symp. on Representations and Methodology of Future Computing Technology, 2003, pp. 191-200.

- [55] P. Zuliani, "Logical Reversibility", IBM J. Res. Develop., Vol. 45, No. 6, 2001, pp. 807-817.