# **Final Solutions** December 6 and 8, 1999

## ECE 171: Introduction to Digital Design Dr. McNames

Write your 6-digit identification number and student identification numbers below. Do not begin the exam or look at the problems until instructed to do so. Once you begin, you have 100 minutes to complete the exam.

Once you begin, write your student ID at the top of each page. This is worth 5 points.

Do not use separate scratch paper. If you need more space, use the backs of the exam pages.

Problem 1: \_\_\_\_\_ / 25

Problem 2: \_\_\_\_\_ / 25

Problem 3: \_\_\_\_\_ / 24

Problem 4: \_\_\_\_\_ / 21

Problem 5: \_\_\_\_\_ / 15

Student ID: \_\_\_\_\_ / 5

Total:\_\_\_\_\_/115

6-Digit Identification Number:

Student Identification Number:\_\_\_\_\_

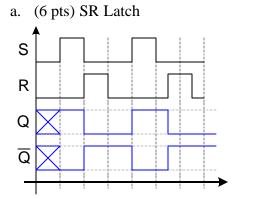

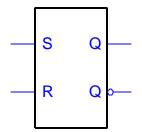

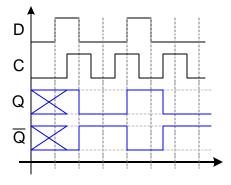

## 1. Latches & Flip Flops (25 Points)

Fill in the timing diagrams and label the symbols for the following latches and flip flops. Assume that the propagation delay is 0.

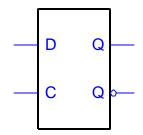

b. (6 pts) D Latch with enable

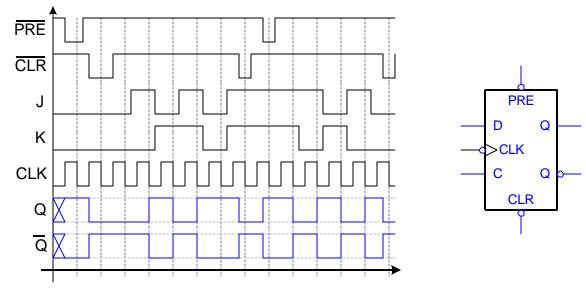

c. (13 pts) JK Flip Flop, falling edge triggered, asynchronous active-low preset and clear.

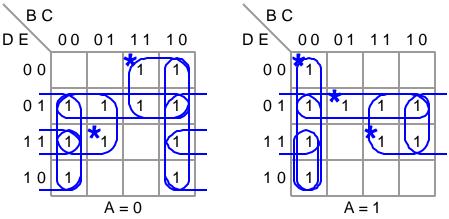

## 2. Five Variable Karnaugh Maps (25 points)

- a. (5 pts) Circle all of the prime implicants for the 5-variable Karnaugh map above.

- b. (4 pts) Put an asterisk (\*) in the <u>upper left</u> corner of each distinguished 1 cell.

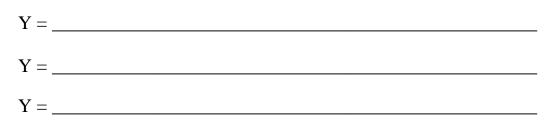

- c. (6 pts) Write the boolean expression for each <u>prime implicant</u> below.

| A'C'D | D'E   | AB'C' |

|-------|-------|-------|

| C'E   | A'BD' | B'C'D |

| A'B'E | A'BC' | ABE   |

- d. (1 pt) How many prime implicants are shared among both 4-variable maps? (Circle one of the options)  $1 \quad 2 \quad \overline{3} \quad 4$

- e. (3 pts) Circle the boolean expression of each essential prime implicant in part c.

- f. (5 pts) Write the expression for each minimal sum of products.

## $\mathbf{Y} = \mathbf{A'B'E} + \mathbf{D'E} + \mathbf{A'BD'} + \mathbf{AB'C'} + \mathbf{ABE} + \mathbf{A'C'D}$

g. (1 pt) How many minimal sums of products are there? Circle one of the options below.

1 2 3 4

#### 3. Logic Gates (24 Points)

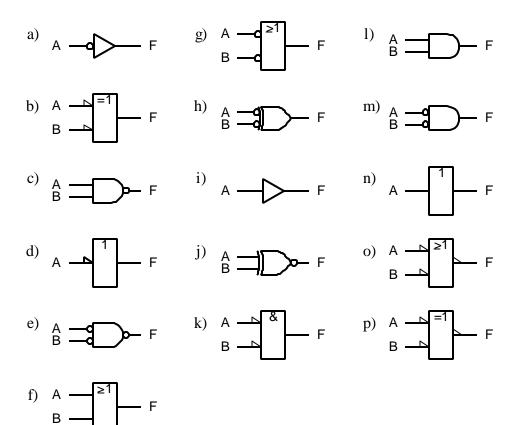

| Boolean<br>Expression                                         | Name of<br>Gate | Standard<br>Symbol | IEEE/ANSI<br>Symbol |

|---------------------------------------------------------------|-----------------|--------------------|---------------------|

| $\mathbf{F} = \overline{\mathbf{A} \oplus \mathbf{B}}$        | XNOR            | j                  | р                   |

| $F = \overline{A} \ \overline{B}$                             | NOR             | m                  | k                   |

| $\mathbf{F} = \overline{\mathbf{A}}$                          | Inverter        | a                  | b                   |

| $F = \overline{\overline{A} + \overline{B}}$                  | AND             | 1                  | 0                   |

| $\mathbf{F}=\overline{\mathbf{A}}\oplus\overline{\mathbf{B}}$ | XOR             | h                  | b                   |

| $\mathbf{F} = \mathbf{A} + \mathbf{B}$                        | OR              | e                  | f                   |

| $F=\overline{A}+\overline{B}$                                 | NAND            | с                  | g                   |

| $\mathbf{F} = \mathbf{A}$                                     | Buffer          | i                  | n                   |

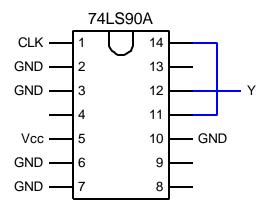

## 4. MSI Devices & Data Sheets (21 points)

Use the supplemental data sheet to answer the following questions about the SN7490A.

- a. (1 pts) How many counters are in this device? (Circle one) 1 2 3 4

- b. (2 pts) What is the count-length (number of distinct states) of each counter? (Circle all that apply) 1 2 3 4 5 6 7 8 9 10

- c. (2 pts) How many flip flops are in this device? (Circle one) 1 2 3 4 5 6 7

8

- d. (2 pts) What is the high noise margin?  $NM_H = 0.4 V$

- e. (1 pt) How are the counter(s) triggered? (Circle one) Rising Edge Falling Edge

- f. (1 pt) What is the maximum clock frequency that could be used to drive <u>any</u> of the counters in this device?  $f_{max} = 16 \text{ MHz}$

- g. (2 pts) What would the outputs be if the inputs R0(1), R0(2), R9(1), and R9(2) where all set high (logic value of 1)? QD = H QC = L QB = L QA = H

- h. (5 pts) Show how the counter could be connected to output a square-wave that is 10 times longer than the clock input. Show how the pins must be connected including the clock input (CLK), power (Vcc), ground (GND), and the output (Y). Some pins may be left unconnected.

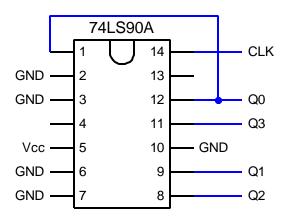

i. (5 pts) Show how the counter could be connected to output a binary count sequence with a count length of 10. Show how the pins must be connected including the clock input (CLK), power (Vcc), ground (GND), and the outputs (Q3, Q2, Q1, and Q0) where Q3 is the most significant bit (MSB). Some pins may be left unconnected.

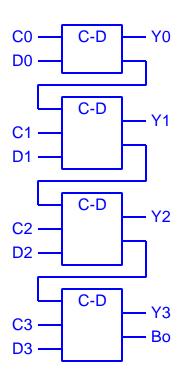

#### **5.** Subtractors (15 points)

A vending machine manufacturer is in need of a 4-bit subtractor. Work through the following problems to design this device.

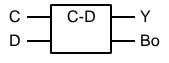

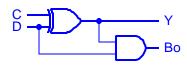

a. (2 pts) For the 2-input subtractor shown below, fill in the truth table. Y is the result of the subtraction (C-D) and Bo indicates whether the subtractor needs to borrow a one from the more significant bit.

| С | D | Y | Bo |

|---|---|---|----|

| 0 | 0 | 0 | 0  |

| 0 | 1 | 1 | 1  |

| 1 | 0 | 1 | 0  |

| 1 | 1 | 0 | 0  |

b. (2 pts) Using as few gates as possible, draw the logic diagram using traditional symbols for the subtractor outputs Y and Bo.

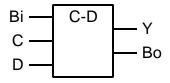

c. (2 pts) For the 3-input subtractor shown below, fill in the truth table. Bi indicates whether the less significant bit needs to borrow a one. Y and Bo are defined the same as in part a.

| С | D | Bi | Y | Bo |

|---|---|----|---|----|

| 0 | 0 | 0  | 0 | 0  |

| 0 | 0 | 1  | 1 | 1  |

| 0 | 1 | 0  | 1 | 1  |

| 0 | 1 | 1  | 0 | 1  |

| 1 | 0 | 0  | 1 | 0  |

| 1 | 0 | 1  | 0 | 0  |

| 1 | 1 | 0  | 0 | 0  |

| 1 | 1 | 1  | 1 | 1  |

## **5. Subtractors Continued**

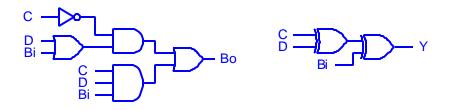

d. (6 pts) Using as few gates as possible, draw the logic diagram using traditional symbols for the outputs Y and Bo of the subtractor in part c..

e. (3 pts) Using the symbols in parts a. and c. draw a logic diagram for a 4-bit subtractor. Label the inputs C3,C2,C1,C0 and D3,D2,D1,D0 where C3 and D3 are the most significant bits. Label the outputs Bo and Y3,Y2,Y1,Y0 where Y3 is the most significant bit.