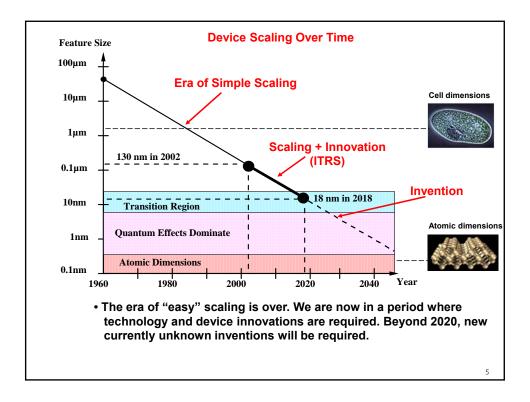

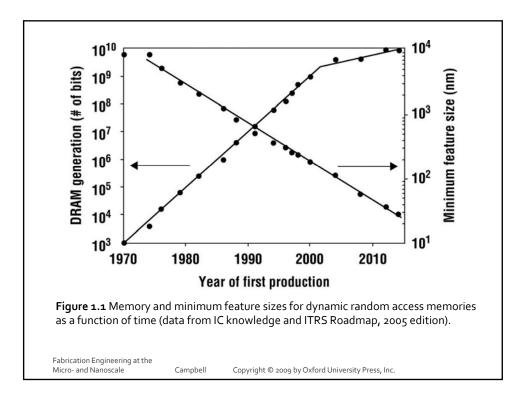

| Year of Production                       | 1998    | 2000    | 2002    | 2004    | 2007    | 2010    | 2013   | 2016    | 2018    |

|------------------------------------------|---------|---------|---------|---------|---------|---------|--------|---------|---------|

| Technology N ode (half pitch)            | 250 nm  | 180 nm  | 130 nm  | 90 nm   | 65 nm   | 45 nm   | 32 nm  | 22 nm   | 18 nm   |

| MPU Printed Gate Length                  |         | 100 nm  | 70 nm   | 53 nm   | 35 nm   | 25 nm   | 18 nm  | 13 nm   | 10 nm   |

| DRAM Bits/Chip (Sampling)                | 256M    | 512M    | 1G      | 4G      | 16G     | 32G     | 64G    | 128G    | 128G    |

| MPU Transistors/Chip (x10 <sup>6</sup> ) |         |         |         | 550     | 1100    | 2200    | 4400   | 8800    | 14,000  |

| Min Supply Voltage (volts)               | 1.8-2.5 | 1.5-1.8 | 1.2-1.5 | 0.9-1.2 | 0.8-1.1 | 0.7-1-0 | 06-0.9 | 0.5-0.8 | 0.5-0.7 |

ITRS at http://public.itrs.net/ (2003 version + 2004 update).

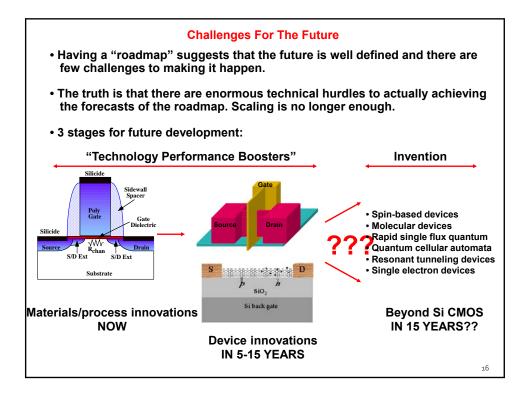

- Assumes CMOS technology dominates over entire roadmap.

2 year cycle moving to 3 years (scaling + innovation now required).

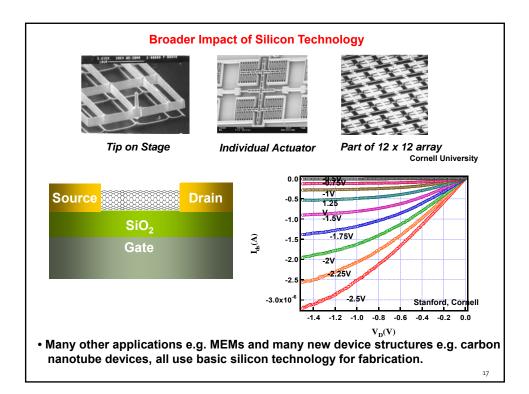

• 1990 IBM demo of Å scale "lithography".

• Technology appears to be capable of making structures much smaller than currently known device limits.