res

OS for optimum speed/power h speed

5 no (00m

5 ns (commercial)

0 ns (military)

power

95 mW (commercial)

60 mW (military)

ROM technology 100% programmable

n 300-mil or standard 600-mil DIP or 28-pin LCC

10% V<sub>CC</sub>, commercial and military

-compatible I/O

ion Guide

um Access Time (ns)

ct replacement for bipolar PROMs

able of withstanding >2001V static discharge

tional Description

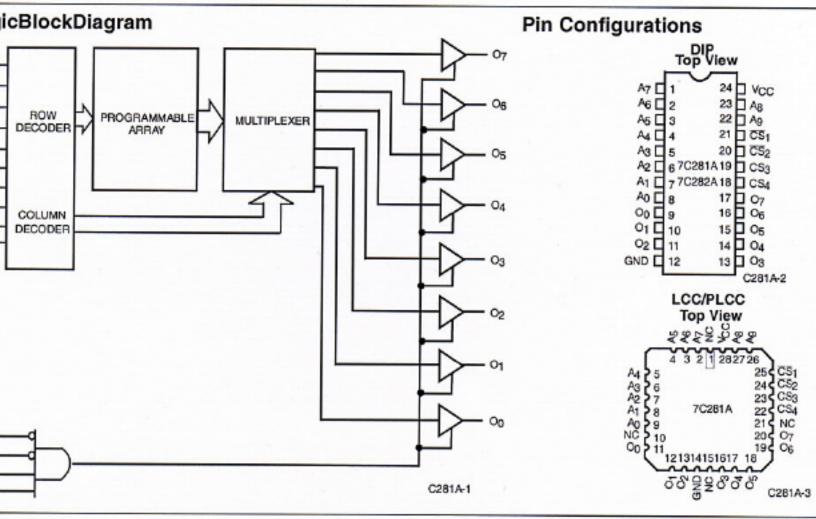

Y7C281A and CY7C282A are high-performance ord by 8-bit CMOS PROMs. They are functionally iden-

tical, but are packaged in 300-mil and 600-mil-wide pa respectively. The CY7C281A is also available in a 28-p less chip carrier. The memory cells utilize proven I floating-gate technology and byte-wide intelligent p ming algorithms.

The CY7C281A and CY7C282A are plug-in replacementary bipolar devices and offer the advantages of lower porperior performance, and programming yield. The EPR requires only 12.5V for the super voltage, and low current quirements allow for gang programming. The EPRC allow each memory location to be tested 100% because location is written into, erased, and repeatedly exercise to encapsulation. Each PROM is also tested for AC mance to guarantee that after customer programming product will meet DC and AC specification limits.

Reading is accomplished by placing an active LOW si  $\overline{\text{CS}}_1$  and  $\overline{\text{CS}}_2$ , and active HIGH signals on  $\text{CS}_3$  and C contents of the memory location addressed by the a lines  $(A_0 - A_9)$  will become available on the output line  $O_7$ ).

7C281A-30

7C282A-30

30

7C281A-45

7C282A-45

7C281A-25

7C282A-25

25