## ECE 271 Midterm #2

Solu

All questions are equally weighted in this open book/open note exam. You are to choose the <u>best</u> answer and mark it on your SCANTRON sheet.

1. All modulo-*n* counter circuits meet the definition of a FSM.

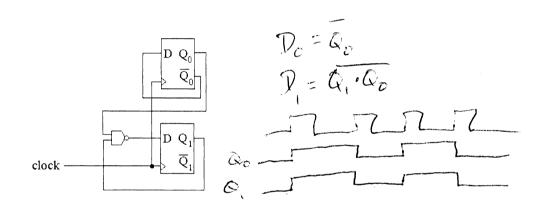

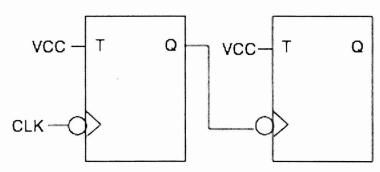

2. Consider the following schematic:

The circuit implements which of the following count sequences?

a.

$$0 \rightarrow 1 \rightarrow 2 \rightarrow 3 \rightarrow 0 \rightarrow ...$$

b.

$$3 \rightarrow 1 \rightarrow 2 \rightarrow 0 \rightarrow 3 \rightarrow ...$$

$$c. \quad 0 \to 2 \to 1 \to 3 \to 0 \to \dots$$

d. none of the above

3. Which type of counter would you expect to operate at a higher frequency?

a. asynchronous counter b. synchronous counter

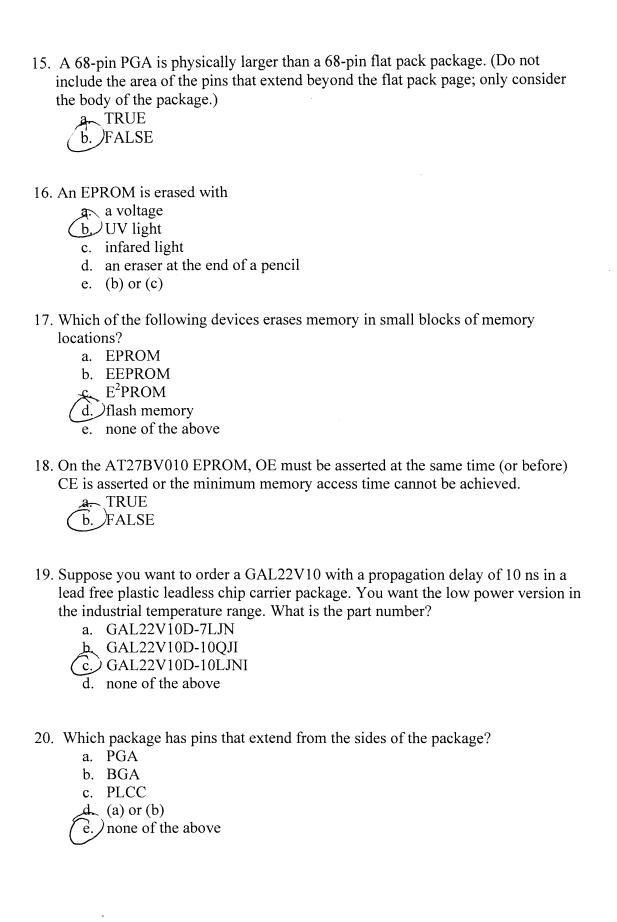

- 5. Which of the following is NOT true concerning the 54LV163 counter

- a. it has a synchronous load function

- b. it is a binary counter

- c. RCO is asserted when the count is maximum

- d.) The two enables are active low.

- 6. One of your classmates says "CLR is the highest priority input on the 54LV163 counter." Do you agree?

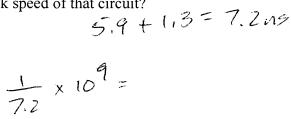

7. A shift register is made with 74LVC2G74 flip-flops operating at VCC = 3.3V. Which of the following is closest to the maximum clock speed of that circuit?

- 8. How can you initialize a counter?

- a. by providing two clock pulses within 2 ns of each other

- b. with a power-on reset circuit

- c. with a manually applied reset pulse

9. You are building a modulo-832 counter using only 54LV163 counters. How many 54LV163 counters are needed?

- d. 16

- e. none of the above

- 10. What is the output value of the counter in problem 9 when CLR on the 54LV163 counters is asserted?

- (a.) 831

- b. 832

- c. 0

- d. none of the above

- 11. The macrocells in a GAL22V10 have a synchronous preset.

- (a.) TRUE

- b. FALSE

- 12. A ring counter is implemented in a PAL16R4-15C. What is the maximum clock speed?

- a. 22 MHz

- کم 27 MHz

- (c.) 37 MHz

- d. 41 MHz

1777

- 13. The count sequence of the above counter is

- (a.)  $0 \rightarrow 1 \rightarrow 2 \rightarrow 3 \rightarrow 0 \rightarrow ...$

- b.  $3 \rightarrow 1 \rightarrow 2 \rightarrow 0 \rightarrow 3 \rightarrow ...$

- c.  $0 \rightarrow 2 \rightarrow 1 \rightarrow 3 \rightarrow 0 \rightarrow ...$

- d. none of the above

- 14. The counter of problem 13 is an example of an asynchronous counter.

- (a) TRUE

- b. FALSE