#### **AC OPERATING CONDITIONS**

TEST CONDITIONS (Test Load and Test Input/Output Reference)

Input pulse level: 0.8 to 2.4V

Input rising and falling time: 5ns

Input and output reference voltage: 1.5V

Output load (See right): CL=100pF+1TTL

CL=50pF+1TTL

1. Including scope and jig capacitance

# **AC CHARACTERISTICS** (Vcc=4.5~5.5V, K6T0808C1D-L Family:Ta=0 to 70°C, K6T0808C1D-P Family:Ta=-40 to 85°C)

| Parameter List |                                 | Symbol |        |     |      |     |       |

|----------------|---------------------------------|--------|--------|-----|------|-----|-------|

|                |                                 |        | 55¹)ns |     | 70ns |     | Units |

|                |                                 |        | Min    | Max | Min  | Max |       |

| Read           | Read cycle time                 | trc    | 55     | -   | 70   | -   | ns    |

|                | Address access time             | taa    | -      | 55  | -    | 70  | ns    |

|                | Chip select to output           | tco    | -      | 55  | -    | 70  | ns    |

|                | Output enable to valid output   | toE    | -      | 25  | -    | 35  | ns    |

|                | Chip select to low-Z output     | tLZ    | 10     | -   | 10   | -   | ns    |

|                | Output enable to low-Z output   | toLz   | 5      | -   | 5    | -   | ns    |

|                | Chip disable to high-Z output   | tHZ    | 0      | 20  | 0    | 30  | ns    |

|                | Output disable to high-Z output | tonz   | 0      | 20  | 0    | 30  | ns    |

|                | Output hold from address change | tон    | 10     | -   | 10   | -   | ns    |

| Write          | Write cycle time                | twc    | 55     | -   | 70   | -   | ns    |

|                | Chip select to end of write     | tcw    | 45     | -   | 60   | -   | ns    |

|                | Address set-up time             | tas    | 0      | -   | 0    | -   | ns    |

|                | Address valid to end of write   | taw    | 45     | -   | 60   | -   | ns    |

|                | Write pulse width               | twp    | 40     | -   | 50   | -   | ns    |

|                | Write recovery time             | twr    | 0      | -   | 0    | -   | ns    |

|                | Write to output high-Z          | twnz   | 0      | 20  | 0    | 25  | ns    |

|                | Data to write time overlap      | tow    | 25     | -   | 30   | -   | ns    |

|                | Data hold from write time       | tрн    | 0      | -   | 0    | -   | ns    |

|                | End write to output low-Z       | tow    | 5      | -   | 5    | -   | ns    |

<sup>1.</sup> The parameter is tested with 50pF test load.

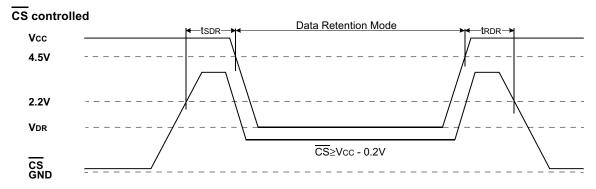

# **DATA RETENTION CHARACTERISTICS**

| Item                                       | Symbol | Test Condition              |        | Min | Тур | Max | Unit |

|--------------------------------------------|--------|-----------------------------|--------|-----|-----|-----|------|

| Vcc for data retention   VDR   CS≥Vcc-0.2V |        |                             | 2.0    | ı   | 5.5 | V   |      |

| Data retention current                     | IDR    | Vcc=3.0V, CS≥Vcc-0.2V       | L-Ver  | -   | 1   | 15  | - μΑ |

| Data retention current                     |        |                             | LL-Ver | -   | 0.2 | 3   |      |

| Data retention set-up time                 | tsdr   | See data retention waveform |        | 0   | -   | -   | ms   |

| Recovery time                              | trdr   |                             |        | 5   | -   | -   |      |

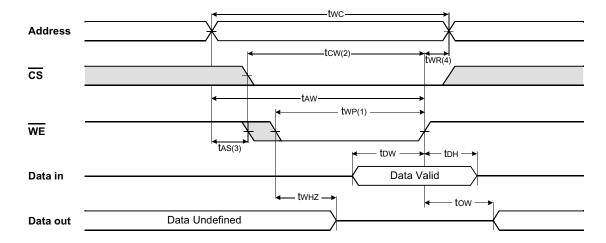

# TIMING WAVEFORM OF WRITE CYCLE(1) (WE Controlled)

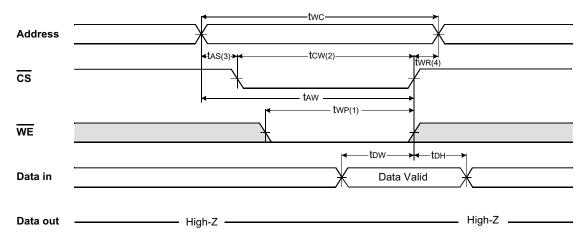

#### TIMING WAVEFORM OF WRITE CYCLE(2) (CS Controlled)

#### NOTES (WRITE CYCLE)

- 1. A write occurs during the overlap of a low  $\overline{\text{CS}}$  and a low  $\overline{\text{WE}}$ . A write begins at the latest transition among  $\overline{\text{CS}}$  going Low and  $\overline{\text{WE}}$  going low: A write end at the earliest transition among  $\overline{\text{CS}}$  going high and  $\overline{\text{WE}}$  going high,  $\overline{\text{twp}}$  is measured from the begining of write to the end of write.

- 2. tcw is measured from the CS going low to end of write.

- 3. tAS is measured from the address valid to the beginning of write.

- 4. twn is measured from the end of write to the address change. twn applied in case a write ends as  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  going high.

# **DATA RETENTION WAVE FORM**