# Microelectronic Test Structures for VLSI Development and Manufacturing

An intensive two-day course March 27-28, 1986 Palo Alto, California

Continuing Education in Engineering,

University Extension,

and the College of Engineering,

University of California, Berkeley

# Microelectronic Test Structures for VLSI Development and Manufacturing

With the advent of very-large-scale integration (VLSI) and ultra-large-scale integration (ULSI), semiconductor processing, as well as packaging, is becoming increasingly complex. A process/package development/monitoring test die is used as the vehicle to move from the initial concept of a basic device to the reliable, reproducible, and economical manufacture of integrated circuits.

This course covers the issues involved in designing a microelectronic test chip. Participants will gain an in-depth understanding of how to design and utilize test structures to develop, define, or debug a new or existing VLSI process, from the basic concept of device structure to the final packaging considerations.

The course is intended for engineers, scientists, and managers interested in developing and maintaining processes and packages for VLSI devices and circuits. It will be of value to semiconductor process and packaging engineers as well as device and circuit designers.

After providing an overview of the field, the course focuses on recent techniques developed to meet the requirements of advanced processes and packages. The first day opens with a general introduction to semiconductor devices and technologies, followed by an examination of packaging considerations. Specific characterization needs, as well as the test structures required for characterization are discussed. Although the course emphasizes silicon integrated circuit applications, the treatment of the subject is useful to those working in other semiconductor fields.

The second day focuses on the design of the test chip for yield and reliability monitoring. Participants are assigned practical problems associated with design.

Time during the course is set aside for discussion and questions. Participants are encouraged to bring specific application problems that they would like to discuss.

Location: Hyatt Rickeys Hotel, 4219 El Camino Real, Palo Alto, California

**Fee: \$495**, including course notes and refreshments and lunch each day. Enrollment is limited and advance enrollment is required. (EDP 323030)

### **Program**

### Thursday, March 27

| 7:45-8:15 am | Registration                                                        |

|--------------|---------------------------------------------------------------------|

| 8:15-8:30    | Introduction / STRATHMAN                                            |

| 8:30-10      | Semiconductor technologies / BHANDIA                                |

| 10-10:30     | Break                                                               |

| 10:30-12     | $\textbf{Devices to circuits: performance benchmarks} \ / \ PERNER$ |

| 12-1 pm      | Lunch                                                               |

| 1-3          | Device characterization / BUEHLER                                   |

| 3-3:30       | Break                                                               |

| 3:30-5       | Packaging / SHIRLEY & BOSE                                          |

### Friday, March 28

5-6

| r riday, March 20 | r riday, Marcii 20                       |  |  |  |

|-------------------|------------------------------------------|--|--|--|

| 8-9 am            | Materials charcterization / STRATHMAN    |  |  |  |

| 9-10              | Reliability in assembly / SHIRLEY & BOSE |  |  |  |

| 10-10:30          | Break                                    |  |  |  |

| 10:30-12          | Yield monitors / BUEHLER                 |  |  |  |

| 12-1 pm           | Lunch                                    |  |  |  |

| 1-2               | Problem sets                             |  |  |  |

| 2-3               | Discussion of problem sets               |  |  |  |

| 3-4               | Panel discussion                         |  |  |  |

Social hour

Continuing Education in Engineering, University Extension, and the College of Engineering, University of California, Berkeley

### Course staff

### Organizer

ALOKE BHANDIA, Staff Engineer, Hewlett-Packard Company, Santa Clara, California

### Instructional staff

ALOKE BHANDIA, Staff Engineer, Hewlett-Packard Company, Santa Clara, California

SUBROTO BOSE, Reliability Engineer, Intel Corporation, Chandler, Arizona

MARTIN BUEHLER, Senior Manager, Technical Services, Jet Propulsion Laboratory, Pasadena, California

FRED PERNER, Manager, Technical Services, Hewlett-Packard Company, Palo Alto, California

GLEN SHIRLEY, Staff Reliability Engineer, Intel Corporation, Chandler, Arizona

MICHAEL STRATHMAN, Manager, RBS Services, Charles Evans & Associates, San Mateo, California

### Faculty adviser

NATHAN CHEUNG, Associate Professor of Electrical Engineering and Computer Sciences, University of California, Berkeley

### **Industry adviser**

MICHAEL STRATHMAN, Manager, RBS Services, Charles Evans & Associates, San Mateo, California

### Program coordinator

LINDA REID, Continuing Education in Engineering University Extension, University of California, Berkeley

### **Enrollment information**

Enrollment is limited and advance enrollment is required. Upon request, a place in the course will be reserved for individuals who require time to obtain authorization. To reserve a place call (415) 642-4151.

### How to enroll

BY MAIL: Fill out and return the enrollment form provided.

BY PHONE: You may enroll by phone if you use Visa or MasterCard; call (415) 642-4111.

Enrollments must be accompanied by the full fee or by purchase order authorization. You may pay by check or use Visa or MasterCard. Make checks payable to the UC Regents.

For efficient processing, we must have your Priority Code, whether you enroll by phone, by mail, or in person. This 5-digit code (3 numbers and 2 letters) appears on the mailing label above the addressee's name. If there is no label on your copy, the code appears in a box in the middle of the address surface

Confirming your enrollment: If you enroll by mail and have not received an enrollment receipt five days prior to the scheduled date of the course, please call (415) 642-4151 to confirm that the course will convene as scheduled. Since UC Extension is self-supporting, it is necessary for us to establish a minimum enrollment. If the minimum is not met at least a week prior to the course date, the course may be canceled; if so, enrollees will be notified.

**Refund policy:** If you enroll and then cannot attend, a refund, less \$20 processing charge, will be granted if requested before the beginning date of the course.

### **Further information**

Housing: A group of rooms will be set aside at the Hyatt Rickeys Hotel, and reservation information will be sent to enrollees. Participants may reserve rooms in advance with Hyatt Rickeys reservation department, (415) 493-8000. Special rates will be available; participants in this course should so identify themselves when requesting room reservations. Reservations must be made no later than February 26, 1986.

Transportation and parking: Regularly scheduled commercial transportation or private limousine service is available between the hotel and the San Francisco and San Jose airports. There is ample free parking at the hotel.

If you have questions, call (415) 642-4151, or write to Continuing Education in Engineering, University Extension, University of California, 2223 Fulton St., Berkeley, CA 94720.

### Forthcoming programs

MOS Analog/Digital Interface Circuit Design for VLSI Digital Systems, January 13-15, 1986, San Francisco Airport

C Language Programming—An Intensive Course, February 13-15, 1986, Berkerley

The C Programming Language—An Introduction, February 20-21, 1986, San Francisco

Composite Materials Workshop, February 24-28, 1986, Berkeley

Workshop on Lisp, March 7-8, 1986, San Francisco

High-Resolution Lithography, March 9, 1986, Santa Clara

UNIX Shell Programming, April 17-19, 1986, Berkeley

Design and Application of Industrial Security Systems, May 6-8, 1986, Berkeley

Workshop on Refractory Metals and Silicides for VLSI IV, May 12-15, 1986, San Juan Bautista

III-V Semiconductor Materials & Devices, June 1986, Palo Alto

Telecommunications Signal Processing and ICs, June 1986, Palo Alto

Materials Characterization Techniques for Integrated Circuit Processing, June 16-19, Palo Alto

6th International Conference on Ion Implantation Technology, July 28-August 1, 1986, Berkeley

Packaging, August 1986, Palo Alto

Barrier Metals, August 1986, Palo Alto

Computer Security Technology, Summer 1986, Berkeley

International Conference on Semiconductor and Integrated Circuit Technology, October 19-26, 1986, Beijing, China

Design and Application of Industrial Security Sytems, December 2-4, 1986, Berkeley

If you would like to receive detailed announcements of any of these programs, please telephone (415) 642-4151, or write to Continuing Education in Engineering, University Extension, University of California, 2223 Fulton St., Berkeley, CA 94720.

# APPLICATION OF TEST CHIPS IN PACKAGING AND ASSEMBLY

C. G. SHIRLEY, S. BOSE, R. C. BLISH !!

INTEL CORPORATION

COMPONENTS ASSEMBLY/TEST

145 SOUTH 79TH ST.

CHANDLER, ARIZONA 85224

- 1. INTRODUCTION

- 2. OVERVIEW OF PACKAGING AND ASSEMBLY

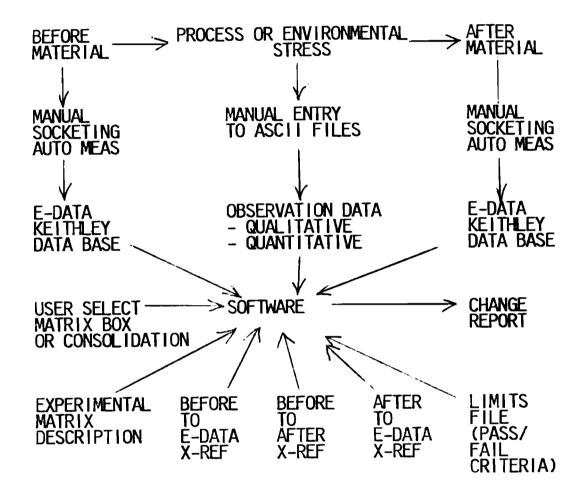

- 3. DATA ANALYSIS SOFTWARE

- 4. SENSOR DESIGN

- 5. DESIGN GUIDELINES

- 6. CASE STUDIES

- 7. DESIGN SOLUTIONS

- 8. BIBLIOGRAPHY

### 1. INTRODUCTION

- O WHAT IS AN "ASSEMBLY" TEST CHIP?

- IT SIMULATES THE MATERIALS AND PROCESSING OF REAL CHIPS, BUT NOT THE LOGICAL FUNCTION.

- IT GIVES ELECTRICAL READOUTS OF CONDITIONS, PAST AND PRESENT, INSIDE THE PACKAGE.

- O TRADITIONALLY ASSEMBLY-RELATED TEST CHIPS HAVE BEEN

- USED TO MEASURE PACKAGE PARAMETERS SUCH AS STRESS, THERMAL IMPEDANCE, AND HUMIDITY.

- USED TO CHARACTERIZE A FEW TENS OF HAND-ASSEMBLED PIECES.

- ASSEMBLED BY A SKILLED PERSON.

- MEASURED USING DESKTOP INSTRUMENTS.

## 1. INTRODUCTION (CONTINUED)

- O TO APPLY TEST CHIPS IN A MANUFACTURING ENVIRONMENT WE ADD THE FOLLOWING OBJECTIVES:

- USE THE TEST CHIPS TO CHARACTERIZE AND QUALIFY NEW WAFER AND ASSEMBLY PROCESSES.

- EXPERIMENTS WILL INVOLVE HUNDREDS OF PIECES TO GIVE A STATISTICAL CHARACTERIZATION OF PROCESSES.

- FACTORY (UNSKILLED) ASSEMBLY SHOULD BE EASY. DESIGN RULES SHOULD BE FOLLOWED.

- USE AN AUTOMATIC PARAMETRIC TESTER WITH SOFTWARE-CONTROLLED SWITCHING MATRIX.

- BUILD A QUALITY AND RELIABILITY DATA BASE BASED ON A FEW WELL-CHARACTERIZED SENSORS.

- O BENEFITS OF THIS NEW ORIENTATION:

- ELIMINATES BOTTLENECKS IN THE SUPPLY OF NEW CHIPS.

- ELIMINATES BOTTLENECKS IN ACCESS TO TESTERS.

- CAN BUILD A DATA BASE FOUNDED ON A WELL-UNDERSTOOD SET OF SENSORS.

- CREATES A COMMON REFERENCE TO AID COMMUNICATION BETWEEN THE WAFER PROCESSING WORLD AND THE ASSEMBLY WORLD. DOES NOT INVOLVE PRODUCT DESIGNERS.

### 2. OVERVIEW OF PACKAGING AND ASSEMBLY

- PACKAGE FAMILIES AND TECHNOLOGIES

- ASSEMBLY PROCESS FLOW

- PACKAGE TESTING

- ASSEMBLY DEFECTS AND RELIABILITY JEOPARDIES

REFERENCE: INTEL QUALITY/RELIABILITY HANDBOOK (ORDER NUMBER 210997-001) INTEL LITERATURE DEPARTMENT, 3065 BOWERS AVE., SANTA CLARA, CA 95051, (800)538-1876, OR (800)672-1833 (CA ONLY). PRICE \$15.

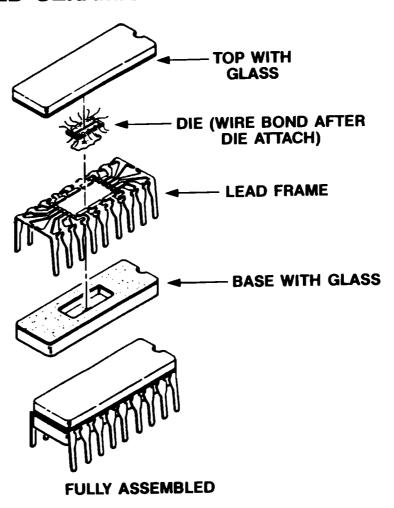

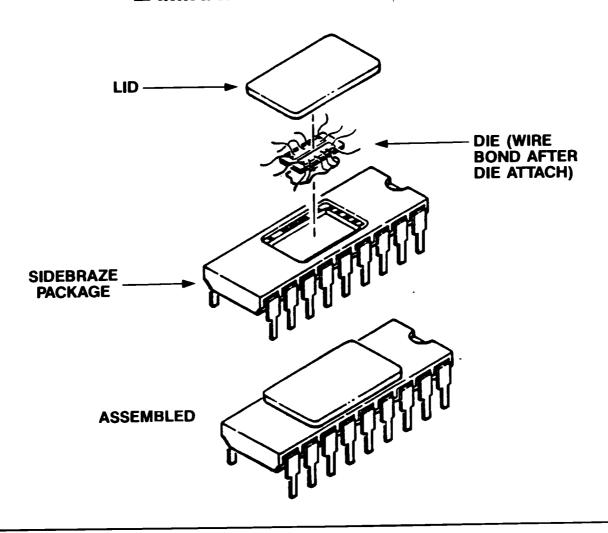

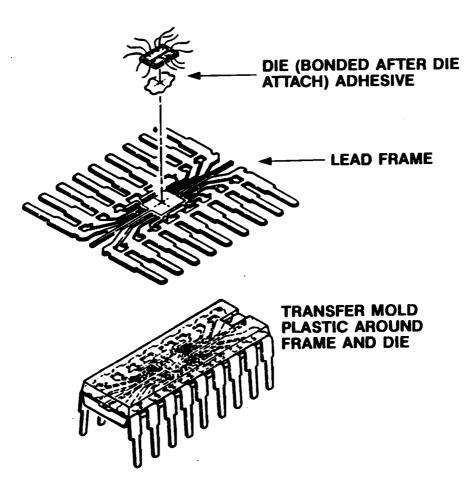

# PACKAGE FAMILIES AND TECHNOLOGIES

## FAMILY AND LEAD COUNT

| TECHNOLOGY                        | DUAL-IN-LINE | CHIP CARRIER | PIN-GRID ARRAY |

|-----------------------------------|--------------|--------------|----------------|

| PRESSED<br>CERAMIC<br>"CERDIP"    | YES, 16-4Ø   | No           | No             |

| LAMINATED<br>CERAMIC<br>"CERAMIC" | YES, 16-48   | YES, 18-68   | YES, 68-132    |

| PLASTIC                           | YES, 16-48   | YES, 18-68   | Under Develpt  |

# intel

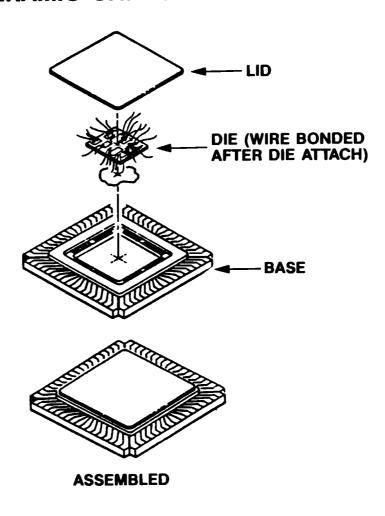

# PRESSED CERAMIC PACKAGE

# LAMINATED CERAMIC PACKAGE

# intel

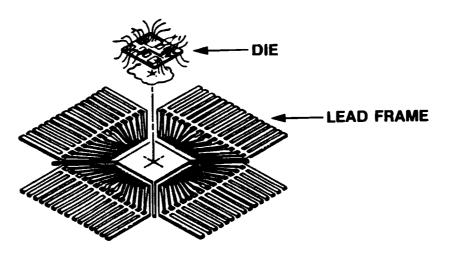

# PLASTIC PACKAGE

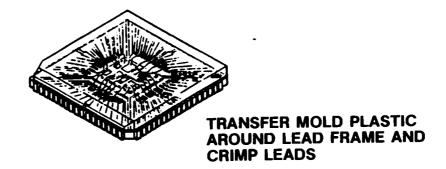

# **CERAMIC CHIP CARRIER**

# **PLASTIC CHIP CARRIER**

# -int<sub>e</sub>l

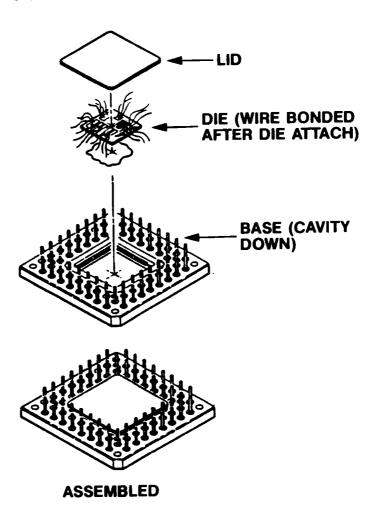

# **PIN GRID ARRAY**

# ASSEMBLY PROCESS FLOW VERSUS PACKAGE TECHNOLOGY

| <br>STEP               | CERDIP                                                                        | CERAMIC                                                                       | <u>PLASTIC</u>                                                           |

|------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| DIE PREP               | Saw<br>Di wash                                                                | SAW<br>DI WASH                                                                | SAW<br>Di wash                                                           |

| INSPECTION             | DIE VISUAL                                                                    | DIE VISUAL                                                                    | DIE VISUAL                                                               |

| DIE ATTACH             | FRAME ATTACH<br>EUTECTIC<br>440 DEG C                                         | EUTECTIC<br>(44Ø DEG C)                                                       | EUTECTIC (44Ø DEG C) OR ADHESIVE (17Ø DEG C, EPOXY. 28Ø DEG C POLYIMIDE) |

| WIRE BOND              | ALUMINUM<br>(ULTRASONIC)                                                      | ALUMINUM<br>(ULTRASONIC)<br>OR GOLD<br>(THERMOSONIC)                          | GOLD<br>(THERMOSONIC)                                                    |

| INSPECTION             | INTERNAL<br>VISUAL GATE                                                       | INTERNAL<br>VISUAL GATE                                                       | ÍNTERNAL<br>VISUAL GATE                                                  |

| ENCAPSULATION          | Oxygen atmos<br>seal, 430 deg<br>11 min                                       | NEUTRAL OR<br>REDUCING ATM<br>36Ø DEG C<br>45 MIN                             | MOLD AT 175 DEG<br>1-2 MIN, CURE<br>175 DEG C, 4 HR                      |

| LEAD FINISH            | TIN PLATE,<br>GOLD PLATE<br>OR SOLDER                                         | AS-RECEIVED<br>GOLD PLATE                                                     | DEFLASH, TRIM<br>AND FORM<br>SOLDER                                      |

|                        | TRIM                                                                          | Trim                                                                          | SINGULATE                                                                |

| INSPECTION             | EXTERNAL<br>VISUAL GATE                                                       | EXTERNAL<br>VISUAL GATE                                                       | EXTERNAL<br>VISUAL GATE                                                  |

| OUTGOING<br>Q.A. TESTS | HERMETICITY CENTRIFUGE LEAD FATIGUE DIE SHEAR BOND LIFT ACOUSTIC OPENS/SHORTS | HERMETICITY CENTRIFUGE LEAD FATIGUE DIE SHEAR BOND LIFT ACOUSTIC OPENS/SHORTS | LEAD FATIGUE BIAS PRESSURE POT  OPENS/SHORTS                             |

|                        |                                                                               |                                                                               |                                                                          |

# PACKAGE TESTING

| <u>Test</u>              | MIL. STD<br>883 | Test Cond                    | DURATION                 | END POINT           | SAM. SIZE         |

|--------------------------|-----------------|------------------------------|--------------------------|---------------------|-------------------|

| HIGH T<br>STORAGE        | 1ØØ8            | 200C D.C<br>200C P<br>200C P | 168 HR<br>48 HR<br>48 HR | E<br>E<br>WIRE PULL | 36Ø<br>36Ø<br>195 |

| TEMP.<br>CYCLE           | 1Ø1ØC           | -55С то 125С<br>С, D, Р      | 1000 CYC                 | EVH                 | 624               |

| Ther <b>mal</b><br>Shock | 1Ø11C           | -65С то 15ØС<br>С. D. Р      | 200 CYC                  | EVH                 | 624               |

| STEAM                    |                 | 121C, 2 ATM<br>C, D, P       | 288 HR                   | E V                 | 624               |

| HUMIDITY                 |                 | 85C, 85% RH<br>C, D, P       | 2000 HR                  | E V                 | 624               |

| SALT ATM                 | 1ØØ9A<br>2ØØ4B  | 35 <b>C</b><br>C, D, P       | 24 HR                    | V, LEAD<br>FATIGUE  | 44Ø               |

| SOLVENTS                 | 2515C           | CHEMICAL<br>C, D, P          | 1 HR                     | V                   | 88                |

| MECH.<br>SHOCK           | 2ØØ2B           | 1.5KG PEAK<br>C, D           | 6 ORIENT                 | H, E                | 165               |

| VIBRATION                | 2007            | 2Ø G PEAK<br>C, D            | 3 ORIENT                 | H, E                | 165               |

| CENTRI-<br>FUGE          | 2ØØ1D           | 20/30 KG<br>C, D             | Z ORIENT                 | H, E                | 5Ø4               |

| Acoustic/<br>PIND        | 2Ø2ØA           | 25Ø Hz<br>C, D               | Z ORIENT                 | н, Е                | 165               |

| DIE<br>ADHERENCE         | 2Ø19            | DIE SHEAR<br>C, D, P         |                          | To destr<br>Force   | 96                |

| WIRE BOND                | 2011            | WIRE PULL<br>C, D, P         |                          | To destr<br>Force   | 156Ø              |

| CAVITY<br>MOISTURE       | 1Ø18            | 100C BAKE<br>C, D            | 1 CYCLE                  | RGA, PPM<br>H2O     | 15                |

| SEAL<br>INTEGRITY        | , 2024          | Torque<br>D                  |                          | To dest<br>Force    | 66                |

# PACKAGE TESTING (CONTINUED)

| Test             | MIL. STD<br>883 | Test Cond               | DURATION | END POINT            | SAM. ŞIZE |

|------------------|-----------------|-------------------------|----------|----------------------|-----------|

| LEAD<br>STRENGTH | 2004            | BEND/FATIGUE<br>C, D, P |          | To DEST<br>No. BENDS | 40        |

| SOLDER-          | 2025            | BEND (C, D, P)          |          | To DESTR<br>Vis      | 228       |

| ABILITY          | 2003            | 100C STEAM<br>C, D, P   | 1 HR     | Vis                  |           |

|                  | -               | 200C BAKE<br>C, D, P    | 5 HR     | Vis                  |           |

KEY: C = CERAMIC, D = CERDIP, P = PLASTIC, E = ELECTRICAL MEASUREMENT, H = HERMETICITY TEST, V = VISUAL

# ASSEMBLY DEFECTS AND PACKAGE RELIABILITY JEOPARDIES

| MODE                | CAUSE                                                                                       | TEST                                           | TECHNOLOGY |

|---------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|------------|

| DIE CRACKING        | DIE ATTACH DEFECT                                                                           | T/C, T/S<br>V, E (CONTINUITY,<br>STRESS)       | C, D, P    |

| DIE OFF             | DIE ATTACH DEFECT                                                                           | V, E(continuity)                               | C, D       |

| THIN FILM CRACKING  | ASSEMBLY DEFECT                                                                             | V, E(CONTINUITY)                               | Р          |

| CAVITY<br>MOISTURE  | LID SEAL DEFECT<br>RESIDUAL GASSES                                                          | RGA, E(TRIPLE TRK)                             | D, C       |

| DIE CORROSION       | IONS FROM PROCESS<br>IONS/MOIST FROM<br>ENV. MOLD/FORM                                      | THB, STEAM, V,<br>E(TRIPLE TRK,<br>CONTINUITY) | P, D       |

| WIRES<br>- ALUMINUM | MACHINE SETUP,<br>MISHANDLING                                                               | BOND PULL<br>Visual                            | D, C       |

| - GOLD              | CORROSION, IMPUR-<br>ITIES IN PLASTIC,<br>SWEEP DUE TO MOLD,<br>OVERHEAT (PURPLE<br>PLAGUE) | BAKE + BOND PULL<br>E(CONTINUITY,<br>KELVIN)   | P, C       |

| PACKAGE             | MOLDING DEFECTS                                                                             | T/S, T/C, V                                    | Р          |

| CRACKS              | DESIGN (GEOMETRY)                                                                           | T/S. T/C, V,H                                  | D, C       |

| SOLDERABILITY       | Oxidation, inter-<br>DIFFUSION, IONIC<br>RESIDUE, ETC.                                      | BAKE + SOLDER<br>STEAM + SOLDER                | P, D, C    |

KEY: P = PLASTIC, D = CERDIP, C = CERAMIC, V = VISUAL, H = HERMETIC, E = ELECTRICAL

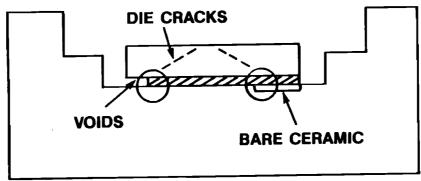

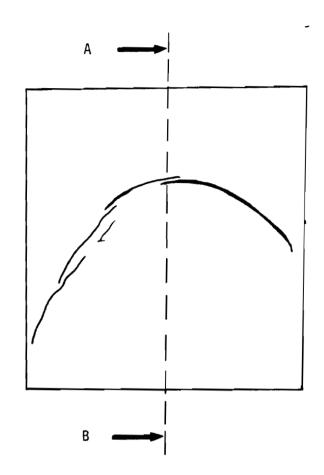

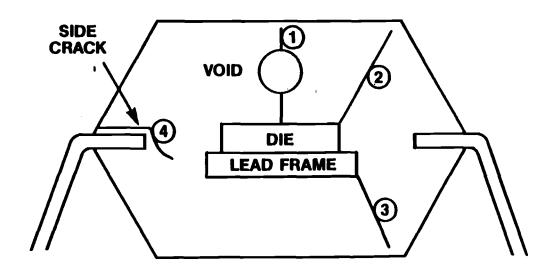

# **CRACKS IN CERAMIC PACKAGES**

**CROSS SECTION VIEW**

### **DIE SURFACE**

# intel

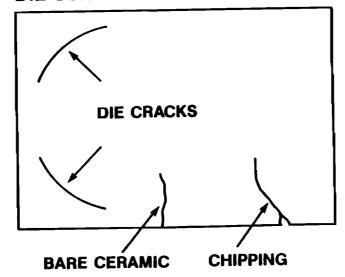

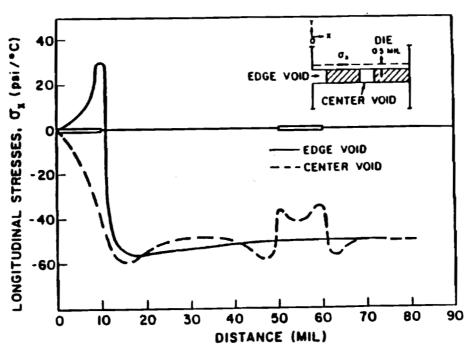

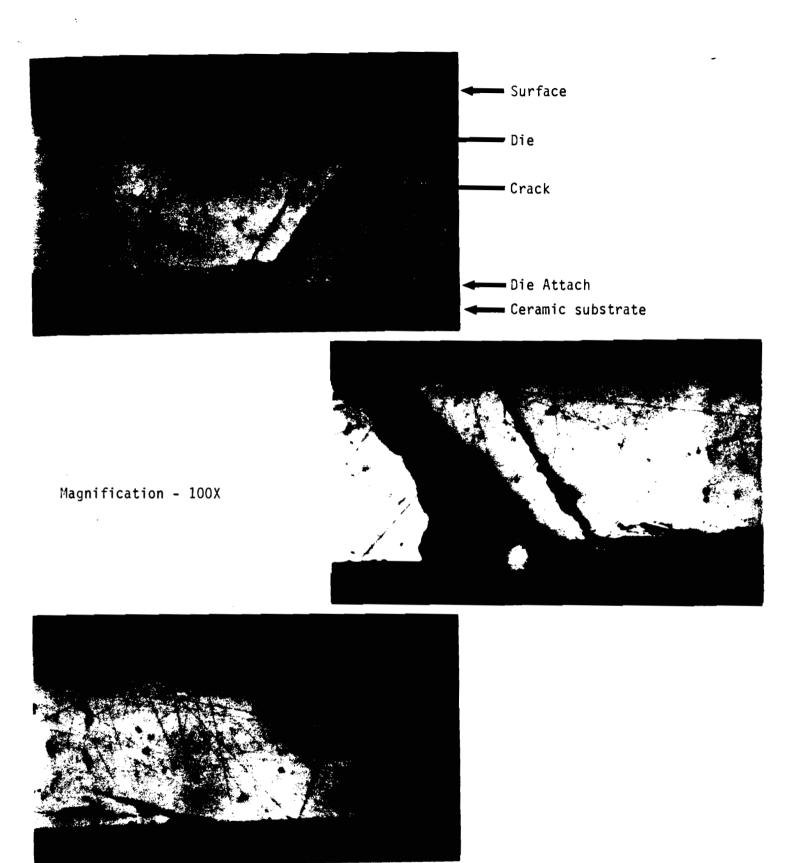

# **DIE CRACKING**

■ EDGE VOIDS (NOT CENTER VOIDS) CAUSE HIGH TENSILE STRESS CONCENTRATION

- FLAWS PRE-EXIST IN THE MATERIAL (BACKSIDE PREPARATION)

- SWAM 1  $\sim$  10 $\mu$ m FLAWSIZE

- DISCO .1  $\sim$  1 $\mu$ m FLAWSIZE

- SMOOTH BACKSIDE IS VERY IMPORTANT

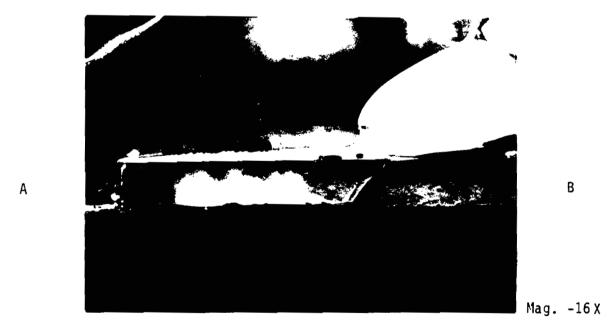

X-Ray Radiograph of unit (#5-6)

Schematic of cracks on the die surface. Arrows indicate the X-Section plane.

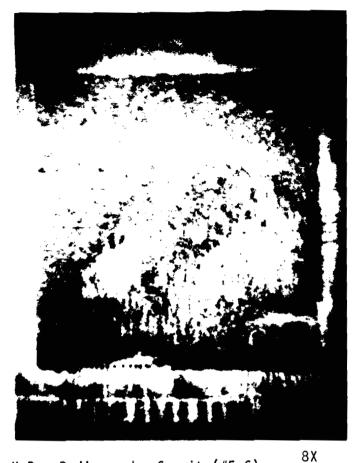

FIGURE 11) Die cross-section of unit #5-6 showing the initiation of the die crack at an edge void/separation.

# COURTESY RAJEN DIAS, INTEL ASSEMBLY/TEST

FIGURE 12) Die cross-section micrographs of unit #5-6 showing die crack initiation at edge voids and propagation to the die surface.

# ASSEMBLY DEFECTS AND PACKAGE RELIABILITY JEOPARDIES

| MODE                | CAUSE                                                                                       | TEST                                           | TECHNOLOGY |

|---------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|------------|

| DIE CRACKING        | DIE ATTACH DEFECT                                                                           | T/C, T/S<br>V, E (CONTINUITY,<br>STRESS)       | C, D, P    |

| DIE OFF             | DIE ATTACH DEFECT                                                                           | V, E(continuity)                               | C, D       |

| THIN FILM CRACKING  | ASSEMBLY DEFECT                                                                             | V, E(CONTINUITY)                               | Р          |

| CAVITY<br>MOISTURE  | LID SEAL DEFECT<br>RESIDUAL GASSES                                                          | RGA, E(TRIPLE TRK)                             | D, C       |

| DIE CORROSION       | IONS FROM PROCESS<br>IONS/MOIST FROM<br>ENV. MOLD/FORM                                      | THB, STEAM, V,<br>E(TRIPLE TRK,<br>CONTINUITY) | P, D       |

| WIRES<br>- ALUMINUM | MACHINE SETUP,<br>MISHANDLING                                                               | BOND PULL<br>VISUAL                            | D, C       |

| – GOLD              | CORROSION, IMPUR-<br>ITIES IN PLASTIC,<br>SWEEP DUE TO MOLD,<br>OVERHEAT (PURPLE<br>PLAGUE) | Bake + BOND PULL<br>E(CONTINUITY,<br>KELVIN)   | P, C       |

| Package<br>cracks   | MOLDING DEFECTS                                                                             | T/S, T/C, V                                    | Р          |

|                     | DESIGN (GEOMETRY)                                                                           | T/S. T/C, V,H                                  | D, C       |

| SOLDERABILITY       | OXIDATION, INTER-<br>DIFFUSION, IONIC<br>RESIDUE, ETC.                                      | BAKE + SOLDER<br>STEAM + SOLDER                | P, D, C    |

KEY: P = PLASTIC, D = CERDIP, C = CERAMIC, V = VISUAL, H = HERMETIC, E = ELECTRICAL

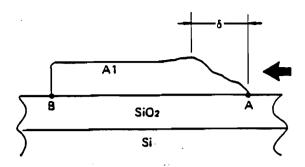

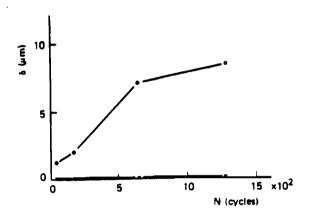

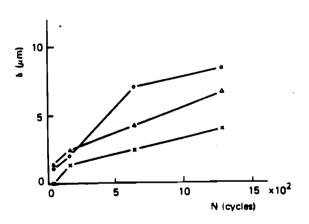

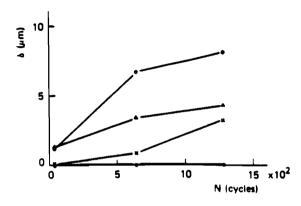

# THIN FILM DEFORMATION IN PLASTIC PACKAGES, REF. 21.

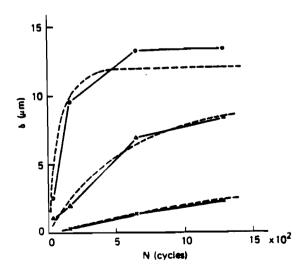

Fig. 4 The effect of molding resins for Al deformation length ( $\delta$ ) versus cycles (N) of thermal shock.

o resin A

x resin B

r = 1,91 mm (Test No. 1)

Fig. 5 The effect of chip sizes for & versus N curves.

- o 2.2 mm x 3.1 mm (r = 1.91 mm)

- △ 2.0 mm x 2.2 mm (r = 1.44 mm)

- x 1.45 mm x 1.8 mm (r = 0.84 mm) (Test No. 2)

Fig. 6. The effect of the overcoatings for  $\delta$  versus N curves.

- o none

- A SiO2

- x polyimide resin

- JCR ( = Junction Coating Resin, silicone varnish )

- r = 1.91 mm (Test No. 3)

Fig. 7 The effect of the temperature differences of thermal shock for δ versus N curves.

- o -65°C≠175°C

- Δ -55°C≠150°C

- × -40°C=125°C

- r = 1,91 mm (Test No. 4)

Dotted line is the theoretical line due to equation (6).

# ASSEMBLY DEFECTS AND PACKAGE RELIABILITY JEOPARDIES

| MODE                | CAUSE                                                                                       | TEST                                           | TECHNOLOGY |

|---------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|------------|

| DIE CRACKING        | DIE ATTACH DEFECT                                                                           | T/C, T/S<br>V, E (CONTINUITY,<br>STRESS)       | C, D, P    |

| DIE OFF             | DIE ATTACH DEFECT                                                                           | V, E(continuity)                               | C, D       |

| THIN FILM CRACKING  | ASSEMBLY DEFECT                                                                             | V, E(CONTINUITY)                               | Р          |

| CAVITY<br>MOISTURE  | LID SEAL DEFECT<br>RESIDUAL GASSES                                                          | RGA, E(TRIPLE TRK)                             | D, C       |

| DIE CORROSION       | IONS FROM PROCESS<br>IONS/MOIST FROM<br>ENV. MOLD/FORM                                      | THB, STEAM, V,<br>E(TRIPLE TRK,<br>CONTINUITY) | P. D       |

| WIRES<br>- ALUMINUM | MACHINE SETUP,<br>MISHANDLING                                                               | BOND PULL<br>VISUAL                            | D, C       |

| - GOLD              | CORROSION, IMPUR-<br>ITIES IN PLASTIC,<br>SWEEP DUE TO MOLD,<br>OVERHEAT (PURPLE<br>PLAGUE) | BAKE + BOND PULL<br>E(CONTINUITY,<br>KELVIN)   | P, C       |

| PACKAGE<br>CRACKS   | MOLDING DEFECTS                                                                             | T/S, T/C, V                                    | Р          |

|                     | DESIGN (GEOMETRY)                                                                           | T/S. T/C, V,H                                  | D, C       |

| SOLDERABILITY       | Oxidation, inter-<br>DIFFUSION, IONIC<br>RESIDUE, ETC.                                      | BAKE + SOLDER<br>STEAM + SOLDER                | P, D, C    |

KEY: P = PLASTIC, D = CERDIP, C = CERAMIC, V = VISUAL, H = HERMETIC, E = ELECTRICAL

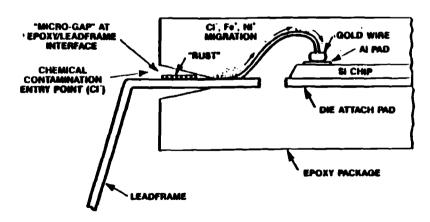

## MODEL FOR BOND PAD CORROSION

CHEMICALS CONTAINING CHLORIDE IONS ENTER THE PACKAGE ALONG THE PLASTIC/LEAD FRAME INTERFACE DUE TO THE INHERENT POOR ADHESION BETWEEN THESE TWO. DURING 85/81 TESTING, CI AND OTHER CONTAMINANTS MIGRATE ALONG THE LEAD FRAME/PLASTIC INTERFACE TO THE GOLD BOND WIRE, TRAVEL UP THE WIRE TO THE BOND PADS WHERE CORROSION PROCEEDS.

MOISTURE PERMEATION MAY PROCEED BY THE SAME MECHANISM OR THROUGH THE BULK EPOXY.

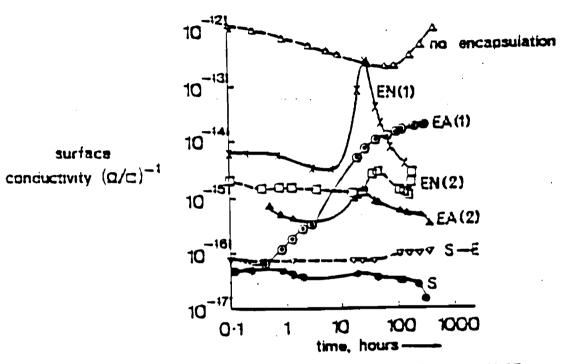

CONTAMINATION ENTRY AND MIGRATION PATH FOR CHLORIDE IONS DURING ASSEMBLY AND THB STRESS THE INFLUENCE OF PLASTIC ENCAPSULATION ON SURFACE CONDUCTIVITY, REF. 22.

FIG 2 EFFECT OF PLASTIC ENCAPSULATION ON SURFACE CONDUCTIVITY, 110°C. 90% RH, 30V (see Table 1 for code identity)

TABLE I

Plastic Encapsulants Used in the Investigation

| Plastic Encapsulant                                                                                 | Code                                         | Aqueous Extract                                    |                               |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------|-------------------------------|

|                                                                                                     |                                              | Conductivity Sm <sup>-1</sup>                      | рН                            |

| Epoxy novolac (1) Epoxy novolac (2) Epoxy anhydride (1) Epoxy anhydride (2) Silicone Silicone-epoxy | EN(1)<br>EN(2)<br>EA(1)<br>EA(2)<br>S<br>S-E | 0.015<br>0.004<br>0.035<br>0.040<br>0.006<br>0.005 | 3.8<br>4.1<br>5.4<br>3.2<br>4 |

# ASSEMBLY DEFECTS AND PACKAGE RELIABILITY JEOPARDIES

| MODE                | CAUSE                                                                                       | TEST                                           | TECHNOLOGY |

|---------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|------------|

| DIE CRACKING        | DIE ATTACH DEFECT                                                                           | T/C, T/S<br>V, E (CONTINUITY,<br>STRESS)       | C, D, P    |

| DIE OFF             | DIE ATTACH DEFECT                                                                           | V. E(continuity)                               | C, D       |

| THIN FILM CRACKING  | ASSEMBLY DEFECT                                                                             | V, E(continuity)                               | Р          |

| CAVITY<br>MOISTURE  | LID SEAL DEFECT<br>RESIDUAL GASSES                                                          | RGA, E(TRIPLE TRK)                             | D, C       |

| DIE CORROSION       | IONS FROM PROCESS<br>IONS/MOIST FROM<br>ENV. MOLD/FORM                                      | THB, STEAM, V,<br>E(TRIPLE TRK,<br>CONTINUITY) | P, D       |

| WIRES<br>- ALUMINUM | MACHINE SETUP,<br>MISHANDLING                                                               | BOND PULL<br>VISUAL                            | D, C       |

| - GOLD              | CORROSION, IMPUR-<br>ITIES IN PLASTIC,<br>SWEEP DUE TO MOLD,<br>OVERHEAT (PURPLE<br>PLAGUE) | E(CONTINUITY,                                  | P. C       |

| PACKAGE<br>CRACKS   | MOLDING DEFECTS                                                                             | T/S, T/C, V                                    | Р          |

|                     | DESIGN (GEOMETRY)                                                                           | T/S. T/C, V,H                                  | D, C       |

| SOLDERABILITY       | OXIDATION, INTER-<br>DIFFUSION, IONIC<br>RESIDUE, ETC.                                      | BAKE + SOLDER<br>STEAM + SOLDER                | P, D, C    |

KEY: P = PLASTIC, D = CERDIP, C = CERAMIC, V = VISUAL, H = HERMETIC, E = ELECTRICAL

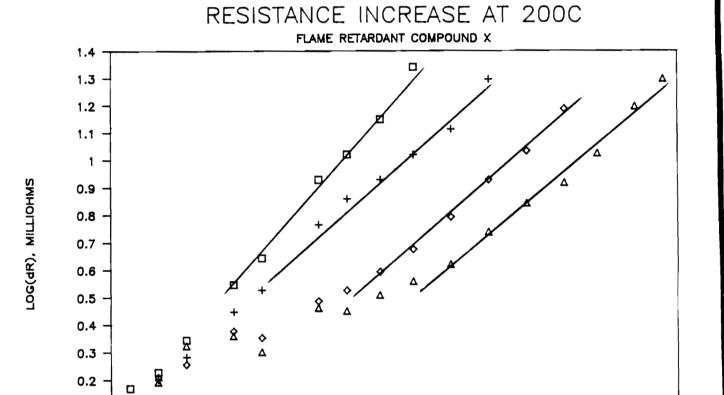

BOND PAD DEGRADATION, REFERENCE 12.

Sectioned Bond - As Encapsulated - R = 0Figure 12

Sectioned Bond - Bake 200 Hrs at 200C - R = 63 mC Figure 13

0.1

2.7wt%Br

0 +

40

GOLD-ALUMINUM WIRBOND CONTACT RESISTANCE VERSUS TIME AT 2000C AND AS A FUNCTION OF BROMINE CONTENT.

COURTESY SYED AHMAD, INTEL ASSEMBLY/TEST

80

TIME, HOURS

60

1.45wt%Br

100

0.8wt%Br

120

140

0.5wt%Br

# ASSEMBLY DEFECTS AND PACKAGE RELIABILITY JEOPARDIES

| MODE                | CAUSE                                                                                       | TEST                                           | TECHNOLOGY |

|---------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|------------|

| DIE CRACKING        | DIE ATTACH DEFECT                                                                           | T/C, T/S<br>V, E (CONTINUITY,<br>STRESS)       | C, D, P    |

| DIE OFF             | DIE ATTACH DEFECT                                                                           | V, E(CONTINUITY)                               | C, D       |

| THIN FILM CRACKING  | ASSEMBLY DEFECT                                                                             | V, E(continuity)                               | Р          |

| CAVITY<br>MOISTURE  | LID SEAL DEFECT<br>RESIDUAL GASSES                                                          | RGA, E(TRIPLE TRK)                             | D, C       |

| DIE CORROSION       | IONS FROM PROCESS<br>IONS/MOIST FROM<br>ENV. MOLD/FORM                                      | THB, STEAM, V,<br>E(TRIPLE TRK,<br>CONTINUITY) | P, D       |

| WIRES<br>- ALUMINUM | MACHINE SETUP,<br>MISHANDLING                                                               | BOND PULL<br>VISUAL                            | D, C       |

| - GOLD              | CORROSION, IMPUR-<br>ITIES IN PLASTIC,<br>SWEEP DUE TO MOLD,<br>OVERHEAT (PURPLE<br>PLAGUE) | BAKE + BOND PULL<br>E(CONTINUITY,<br>KELVIN)   | P, C       |

| PACKAGE             | MOLDING DEFECTS                                                                             | T/S, T/C, V                                    | Р          |

| CRACKS              | DESIGN (GEOMETRY)                                                                           | T/S. T/C, V,H                                  | D, C       |

| SOLDERABILITY       | OXIDATION, INTER-<br>DIFFUSION, IONIC<br>RESIDUE, ETC.                                      | BAKE + SOLDER<br>STEAM + SOLDER                | P, D, C    |

KEY: P = PLASTIC, D = CERDIP, C = CERAMIC, V = VISUAL, H = HERMETIC, E = ELECTRICAL

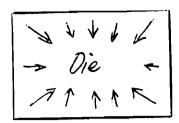

# STRESS IN PLASTIC PACKAGES

### FAILURE MECHANISM DRIVEN BY STRESS CONCENTRATIONS

- VOID—STRESS CONCENTRATOR

- DIE/PAD CORNER—THERMAL MISMATCH

- **—GEOMETRIC DISCONTINUITY**

- SIDE CRACKS—POOR LEAD FRAME/MOLDING COMPOUND ADHESION

- **—LEAD FRAME DESIGN**

- **—DTF OPERATION**

intel

### **MOLDING VOIDS**

$\boldsymbol{e}_{i}^{k}.$

- **VOIDS CREATED DURING MOLDING OPERATION**

- STRESS CONCENTRATIONS ARISE AROUND VOIDS DUE TO DISCONTINUITY

- TEMPERATURE CYCLING OF PLASTIC PACKAGES CAUSES CRACKS TO FORM AND PROPOGATE UP TO THE SURFACE AND DOWN TO THE DIE

WHEN A VOID EXISTS INSIDE A PLATE UNDER A UNIFORM STRESS FIELD  $\sigma_{x}$  (a  $\lessdot$  b)

$$\sigma_{x} = \left\langle \begin{array}{c} A \\ \hline \\ B \end{array} \right\rangle \stackrel{A}{\Longrightarrow} \sigma_{x}$$

THE STRESS AT POINT A AND B CAN BE AS HIGH AS 3  $\sigma_{\rm x}$

# 3. DATA ANALYSIS SOFTWARE

# 4. SENSOR DESIGN

- THERMAL

- KELVIN

- CONTINUITY

- WIRE LOCATION

- STRAIN

- CORROSION AND/OR MOISTURE

### THERMAL ELEMENT DESIGN

### **THEORY:**

TO MEASURE THERMAL IMPEDANCE OF PACKAGE, DISSIPATE A KNOWN AMOUNT OF POWER, AND MEASURE THE CORRESPONDING TEMPERATURE RISE.

THERMAL IMPEDANCE = (TJ - Tc)/P,

WHERE TJ IS THE JUNCTION TEMPERATURE AND TC IS THE CASE TEMPERATURE. TJ - TC IS DETERMINED BY USING A CONSTANT CURRENT TO FORWARD BIAS A DIODE (AT NEGLIGIBLE POWER) AND BY MONITORING THE VOLTAGE ACROSS IT. I=IS[EXP(V/kT)-1] BECOMES V=CONSTANT X T. THE CONSTANT IS DETERMINED BY CALIBRATION IN A THERMAL BATH. THE POWER, P, IS DETERMINED BY MEASURING THE CURRENT THROUGH AND VOLTAGE ACROSS A HEATER ELEMENT. THE HEATER AND THE DIODE CAN BE THE SAME, OR SEPARATE:

SEE REF. 1 FOR REVIEW AND SEE REF. 4 FOR MEASUREMENT GUIDELINES.

### DESIGN GUIDELINES:

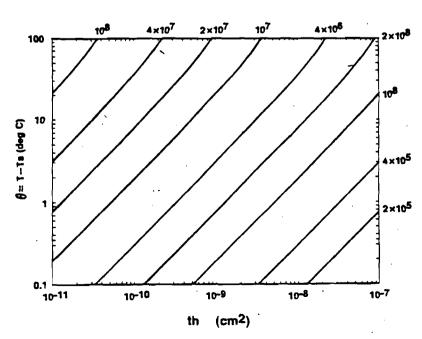

O CURRENT DENSITY IN AL LESS THAN 1xE5 AMP/CM2.

Two reasons: ELECTROMIGRATION, THROUGH-FILM TEMPERATURE PROFILES. REF. 5

T = METAL THICKNESS

H = DIELECTRIC THICKNESS

DIELECTRIC = THERMAL SIO2

# THERMAL ELEMENT DESIGN (CONTINUED)

- O CURRENT DENSITY IN AL CONTACTS LESS THAN 1XE5 AMP/CM^2.

- O VOLTAGE LESS THAN 10 VOLTS BETWEEN PINS.

- O CURRENT IN WIRES LESS THAN 100 MA/WIRE.

- O CAPABILITY OF CAUSING A TEMPERATURE RISE OF 20 DEG C.

- O MAXIMUM POWER DISSIPATION OF ABOUT 4 WATTS/CM2.

- O USE SEPARATE HEATER AND SENSOR.

- O USE POLYSILICON HEATER (NO JUNCTION PROBLEMS).

- O KEEP RESISTANCE OF DIODE INTERCONNECTS NEGLIGIBLE.

- O SEPARATION OF HEATER AND SENSOR LESS THAN 2 MILS (REF. 1).

# THERMAL ELEMENT DESIGN (CONTINUED)

### **EXAMPLE:**

SIMULATE A 400 MIL SQUARE CHIP DISSIPATING AT LEAST 4 WATTS. THE CHIP IS MADE OF IDENTICAL MODULES 50 MILS SQUARE. DESIGN A POLYSILICON HEATER.

DISSIPATION PER CELL >  $4/64 = \emptyset.0625$  WATTS = PCELL

ONE WIRE IN, ONE OUT, SO IMAX = 100 MA

Total voltage drop across chip < 10 V, so for module, Vmax = 10/8 = 1.25 V

SO

PCELL/IMAX^2 < R < VMAX^2/PCELL,

OR

6.25 OHMS < R < 25 OHMS.

POLYSILICON, OR DIFFUSIONS HAVE TYPICALLY 10 - 20 OHMS/SQUARE. SO MAKE THE HEATER ONE SQUARE OF POLYSILICON.

## PROBLEM:

COULD ALUMINUM BE USED AS A HEATER?

### PROBLEM:

COULD ALUMINUM BE USED AS A HEATER?

### ANSWER:

ALUMINUM TYPICALLY HAS A SHEET RESISTANCE OF 0.05 OHMS/SQUARE (AND THICKNESS OF 1.2 MICRONS), SO WE'D NEED 125-500 SQUARES OF ALUMINUM. FOR 100MA AND 1.2 MICRONS OF ALUMINUM, THE MINIMUM LINEWIDTH IS ROUGHLY 85 MICRONS TO PREVENT ELECTROMIGRATION (1XE5 A/CM^2 CURRENT LIMIT), AND STEEP THROUGH-FILM TEMPERATURE VARIATIONS. THE TOTAL AREA OF ALUMINUM REQUIRED IS THEREFORE AT LEAST 125 X (85/25.4)2 = 1400 SQUARE MILS. THIS COMPARES WITH 2500 SQUARE MILS AVAILABLE ON THE MODULE.

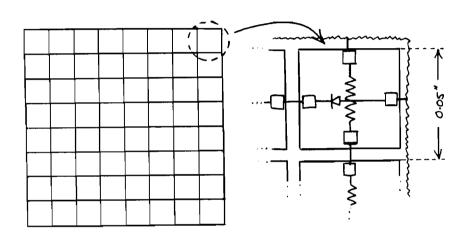

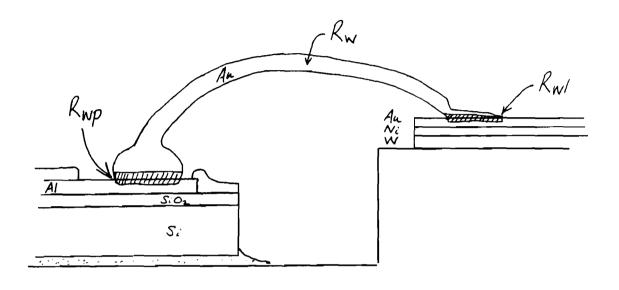

# KELVIN WIRE RESISTANCE MEASUREMENTS

### **THEORY:**

THERE ARE THREE RESISTANCES OF INTEREST FOR ANY WIRE:

TYPICALLY, RWP OR RWL WILL INCREASE AS THE WIRE/PAD OR WIRE/LEAD FINGER INTERFACE DEGRADES UNDER ENVIRONMENTAL STRESS. IT IS DESIRABLE TO MEASURE CHANGES IN THESE INTERFACIAL RESISTANCES SEPARATELY.

TO MEASURE CHANGES IN RWP OR RWL, WE NEED

- (1) A NUMBER OF BOND PADS SHORTED TOGETHER, OR A SHEET OF ALUMINUM.

- (II) GROUPS OF LEAD FINGERS BONDED TO THE SHEET.

- (III) AT LEAST 4 LEAD FINGERS BONDED TO EACH OTHER.

# KELVIN WIRE RESISTANCE MEASUREMENTS (CONTINUED)

FOR, EXAMPLE, FORCE CURRENT THROUGH PIN 1, WITHDRAW THROUGH PIN 3, AND MEASURE THE VOLTAGE BETWEEN PINS 4 AND 5. THIS GIVES THE RESISTANCE OF BOND X AS

Rx = Rxw + RxwL + RxwP

Now force current into Pin 18 and Withdraw it from Pin 17 and measure the voltage between Pins 16 and 19. This gives the resistance of the Bond Y As

RY = RYW + 2RYWL

COMPUTE R.

R = Rx - Ry/2 = Rxw - Ryw/2 + Rxwp

RXW AND RYW WILL CHANGE LITTLE WITH ENVIRONMENTAL STRESS, SO CHANGES IN R WILL BE A GOOD MEASURE OF CHANGES IN THE INTERFACIAL RESISTANCE RXWP. WE HAVE ASSUMED THAT RXWL = RYWL.

GOOD TECHNIQUE WOULD UTILIZE A HIGH-RESOLUTION DVM, AND A CONSTANT CURRENT SOURCE. TYPICAL RESISTANCES MEASURED WOULD BE 180 MILLIOHMS, AND RESOLUTION NEEDED IS 1 MILLIOHM. IF A CURRENT OF 100 MA IS FORCED, THE VOLTAGE RESOLUTION NEEDED IS 100 MICROVOLTS.

#### PROBLEMS:

How would one measure Rwp directly, without having to correct for RwL?

WHAT HAPPENS IF THE BOND PADS ARE CONNECTED BY INTERCONNECT OF APPRECIABLE RESISTANCE?

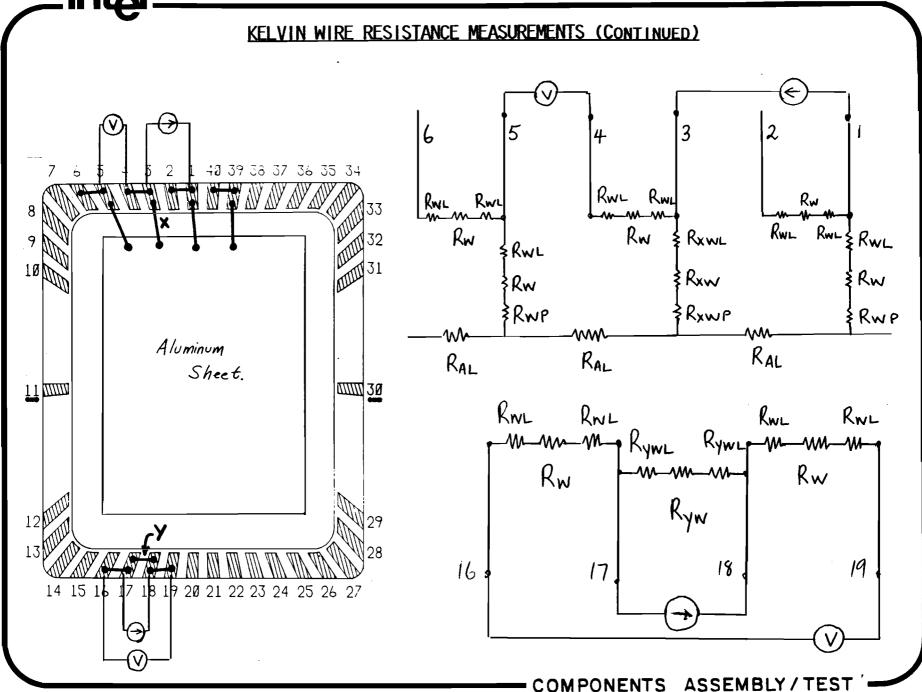

# CONTINUITY SENSOR

### PROBLEM:

HOW BIG A CRACK IN AN INTERCONNECT BEFORE THERE IS A DETECTABLE INCREASE IN RESISTANCE?

#### THEORY:

SOLVED BY CONFORMAL MAPPING BY P. M. HALL, REF. 13. THE NUMBER OF EXTRA SQUARES DUE TO A CRACK IS GIVEN BY

NUMBER OF EXTRA SQUARES = (4/PI)LN[SEC(PI\*E/2)]

WHERE E IS THE CRACK LENGTH AS A FRACTION OF THE LINEWIDTH. A GOOD RULE OF THUMB: 70% CRACKED GIVES ONE EXTRA SQUARE.

LONG, NARROW SENSORS ARE ONLY DETECTED AS GOOD, OR OPEN.

COMPONENTS ASSEMBLY/TEST

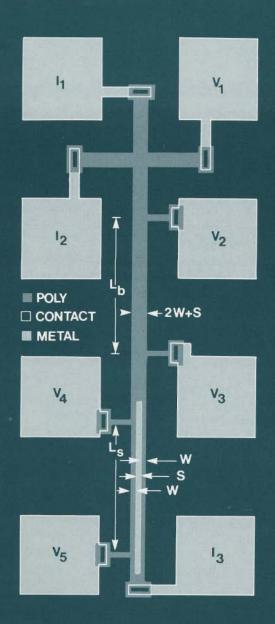

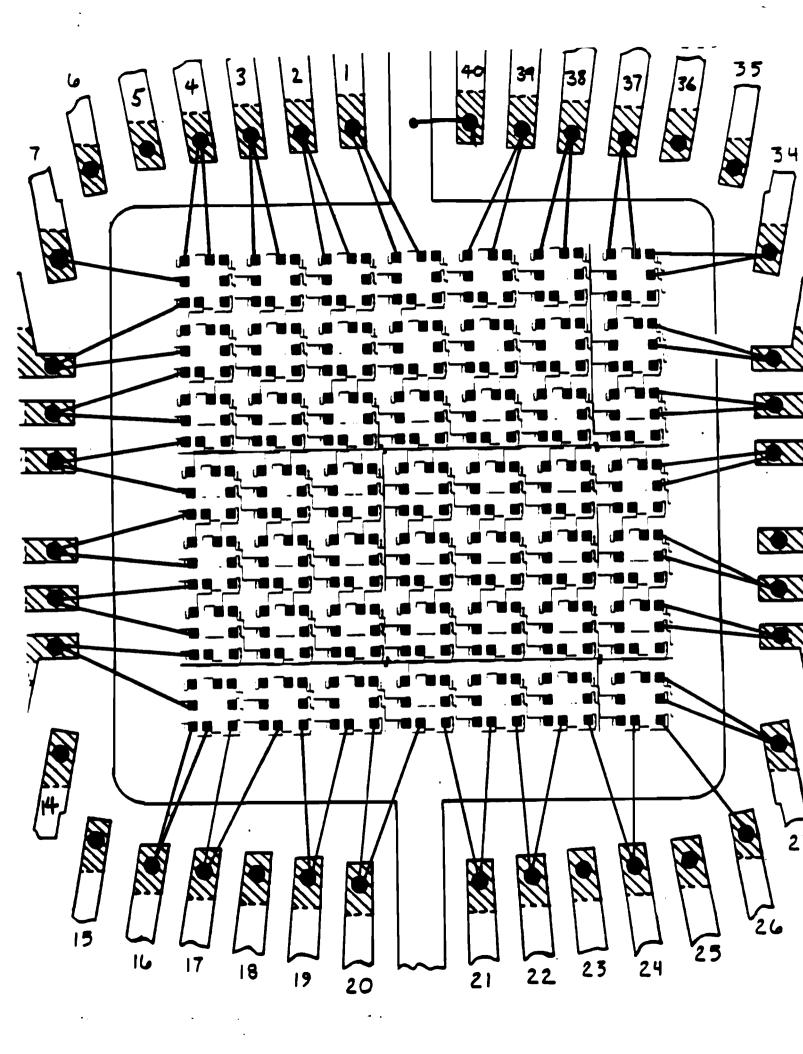

# WIRE BOND POSITION SENSOR

### MOTIVATION:

VISUAL MEASUREMENTS OF WIRE-BOND LOCATION ON BOND PADS ARE TEDIOUS. ELECTRICAL TECHNIQUE IS MORE CONVENIENT, ESPECIALLY IF LARGE NUMBERS OF WIRE-BOND LOCATIONS ARE TO BE DETERMINED.

### METHOD:

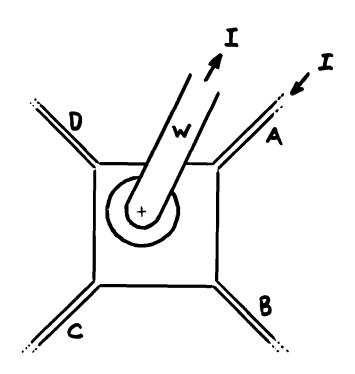

A POSITION-SENSITIVE PAD HAS ELECTRICAL CONNECTION TO EACH OF ITS CORNERS AS SHOWN:

CURRENT IS FORCED INTO CORNER A, AND WITHDRAWN THROUGH THE WIRE, W. THE POTENTIAL DIFFERENCE IS MEASURED BETWEEN CORNERS B AND D. NOW REPEAT, BY CYCLIC PERMUTATION OF A, B, C AND D. THE RESULTING FOUR RESISTANCES (OVER-) DETERMINE THE LOCATION OF THE BALL.

# WIRE BOND POSITION SENSOR (CONTINUED)

### **THEORY:**

THE THEORY IS STRAIGHT-FORWARD FOR THE CASE OF AN INFINITE SHEET OF ALUMINUM WITH CONTACTS ARRANGED IN A SQUARE (AT POSITIONS A, B, C, AND D) AND WITH THE CENTROID OF THE BALL AT W. ELEMENTARY THEORY GIVES THE POTENTIAL DIFFERENCE (EXPRESSED AS RESISTANCE) BETWEEN B AND D DUE TO THE SOURCE AT A AS

$RBD(\underline{A}) = (RHO/2*PI)*LN(|\underline{B}-\underline{A}|/|\underline{D}-\underline{A}|) = \emptyset$

WHEREAS THE POTENTIAL DIFFERENCE DUE TO THE SINK AT THE WIRE IS

$RBD(\underline{W}) = -(RHO/2*PI)*LN(|\underline{B}-\underline{W}|/|\underline{D}-\underline{W}|).$

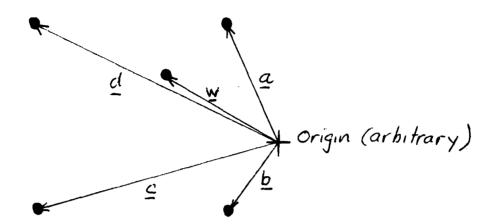

So the total potential difference is RBD = RBD(W) + RBD(A) = RBD(W). Define

KBD = EXP(4\*Pi\*RBD/RHO)

THEN THE LOCUS OF W CORRESPONDING TO A CONSTANT VALUE OF RBD IS GIVEN BY

|D-W|/|B-W| = SQRT(KBD)

THIS LOCUS IS A SET OF CIRCLES OF RADIUS 2\*SQRT(K)/IK-11 AND CENTER (K+1/K-1,Ø), REFERRED TO THE COORDINATES SHOWN ABOVE. A SIMILAR SET OF LOCI CAN BE DRAWN FOR EACH OF THE OTHER 3 MEASUREMENTS. WHEN THESE ARE SUPERIMPOSED WE PRODUCE A SET OF COORDINATES BY WHICH THE BALL CAN BE LOCATED.

# WIRE BOND POSITION SENSOR (CONTINUED)

### PROBLEMS:

DERIVE THE FOUR-POINT PROBE FORMULA FOR AN INFINITE SHEET.

DERIVE THE LOCUS SHOWN ABOVE.

SKETCH HOW THE "EQUIPOTENTIALS" WILL BE CHANGED IF THE BOND PAD IS FINITE; IF THE BALL IS NOT A POINT SOURCE/SINK.

WHAT INSTRUMENTS ETC. (RESOLUTION, AMOUNT OF CURRENT ETC.) IS NECESSARY TO MAKE THIS MEASUREMENT.

WHAT IS THE EFFECT OF THE WIRE RESISTANCE, THE RESISTANCES OF THE CONTACTS TO THE CORNERS OF THE BOND PADS?

# STRAIN GAUGE DESIGN

### **PURPOSE:**

STRAINS ARE INTRODUCED INTO CHIPS THROUGHOUT THE PROCESSING CYCLE, BUT THE LARGEST STRAINS ARE INTRODUCED DURING ASSEMBLY. THE MAIN SOURCES OF STATIC STRAIN ARE INTRODUCED AT DIE-ATTACH DUE TO THERMAL COEFFICIENT MISMATCH BETWEEN SUBSTRATE AND DIE, AND AT SEAL DUE TO ENCAPSULATION IN PLASTIC PACKAGES. DYNAMIC STRAINS ALSO OCCUR DURING THE THERMAL CYCLING AND SHOCK NEEDED TO QUALIFY PACKAGES. THE PIEZORESISTANCE PHENOMENON IN SILICON PROVIDES AN OPPORTUNITY TO MEASURE THESE STRAINS.

## THEORY:

THE PIEZORESISTANCE PHENOMENON COUPLES THE FRACTIONAL CHANGE IN RESISTANCE IN THE I DIRECTION TO THE NORMAL  $\sigma$  AND SHEAR TIMPOSED STRESSES FOR CUBIC CRYSTALS SUCH AS SILICON VIA THREE FUNDAMENTAL PIEZORESISTANCE COEFFICIENTS,  $\widetilde{\pi}_{ll}$ ,  $\widetilde{\pi}_{l2}$ ,  $\widetilde{\pi}_{44}$ :

$$\frac{\Delta R}{R}\Big|_{i} = \widetilde{\mathcal{H}}_{i,1} \, \mathcal{T}_{1} + \widetilde{\mathcal{H}}_{i,2} \, \mathcal{T}_{2} + \widetilde{\mathcal{H}}_{i,3} \, \mathcal{T}_{3} + \widetilde{\mathcal{H}}_{i,4} \, \mathcal{C}_{23} + \widetilde{\mathcal{H}}_{i,5} \, \mathcal{T}_{i,3} + \widetilde{\mathcal{H}}_{i,6} \, \mathcal{T}_{i,2} \, (1)$$

WHERE I = 1,2,3. NOTE THAT THE PIEZORESISTANCE COEFFICIENTS HAVE THE FOLLOWING PROPERTIES WHEN 1, 2, AND 3 ARE THE CUBIC AXES:

$$\begin{split} \widetilde{\Pi}_{i1} &= \widetilde{\Pi}_{22} = \widetilde{\Pi}_{33}, \ \widetilde{\Pi}_{i2} = \widetilde{\Pi}_{i3} = \widetilde{\Pi}_{23}, \ \widetilde{\Pi}_{ij} = \widetilde{\Pi}_{ji}, \\ \widetilde{\Pi}_{44} &= \widetilde{\Pi}_{55} = \widetilde{\Pi}_{66}, \ \widetilde{\Pi}_{56} = \widetilde{\Pi}_{45} = \widetilde{\Pi}_{4\epsilon} = 0. \end{split}$$

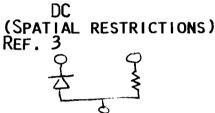

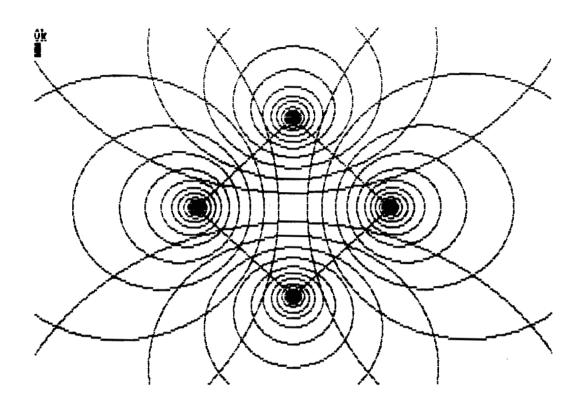

IT IS USEFUL TO HAVE A FEEL FOR THE WAY IN WHICH VARIES WITH COMPOSITION AND TEMPERATURE. THEORY SHOWS (SEE, EG. REF. 14.) THAT

$$\widetilde{\pi}_{ij} = Q_{ij} P(N, T)$$

(2)

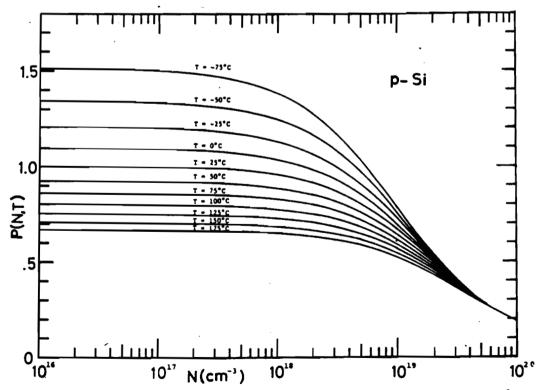

Fig. 8. Piezoresistance factor P(N, T) as a function of impurity concentration and temperature for n-Si.

Fig. 9. Piezoresistance factor P(N, T) as a function of impurity concentration and temperature for p-Si.

#### NOTICE THAT

- (1) THE TEMPERATURE EFFECT BECOMES LESS WITH INCREASING DOPING, BUT IS STILL SIGNIFICANT (ABOUT Ø.2 % PER DEGREE C) AT CONCENTRATIONS OF INTEREST (1xE19 TO 1xE2Ø /cm^3).

- (II)  $\widetilde{\mathcal{H}_{i,j}}$  BECOMES LESS WITH INCREASING TEMPERATURE AND DOPING.

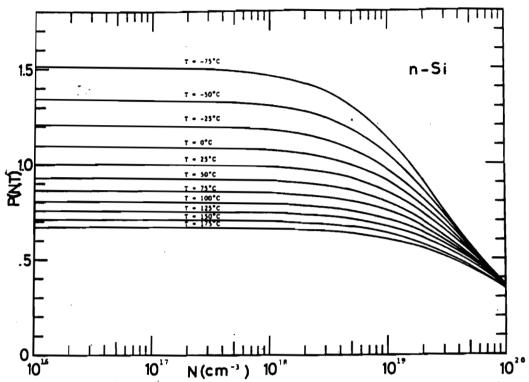

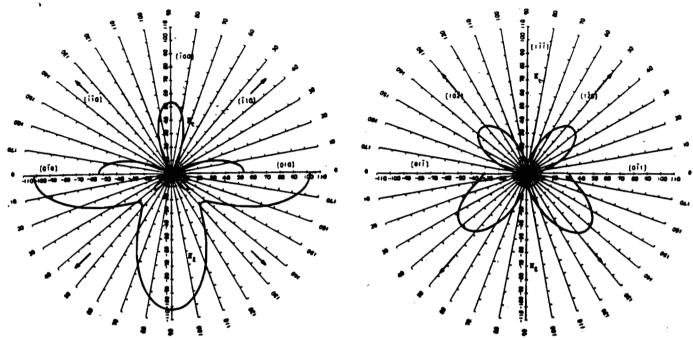

THE DIRECTIONAL ASPECTS OF THE PIEZORESISTIVE PHENOMENON MAY BE STUDIED BY CONSIDERING THE RESPONSE OF A DIFFUSED RESISTOR TO LONGITUDINAL AND TRANSVERSE TENSILE STRESSES AS IT IS IMAGINED TO ROTATE IN A GIVEN CRYSTAL PLANE. REF. 14 HAS SOME NICE POLAR PLOTS...

Fig. 2. Room temperature piezoresistance coefficients in the (001) Fig. 4. Room temperature piezoresistance coefficients in the (211) plane of n-Si (10<sup>-12</sup> cm<sup>2</sup>/dyne).

Fig. 3. Room temperature piezoresistance coefficients in the (011) Fig. 5. Room temperature piezoresistance coefficients in the (001) plane of n-Si (10<sup>-12</sup> cm<sup>2</sup>/dyne).

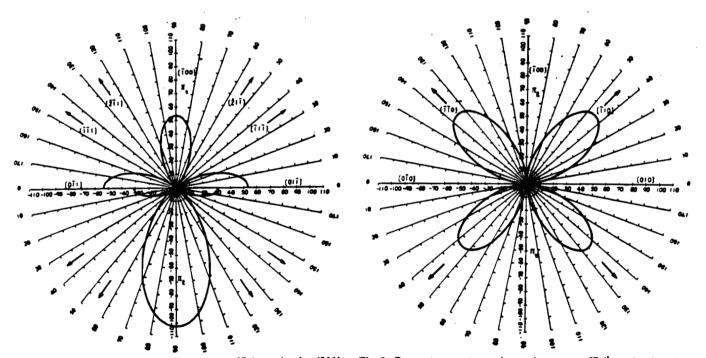

# **APPLICATION:**

TYPICALLY, ONE USES THREE OR FOUR RESISTORS ALIGNED ALONG MAJOR CRYSTALLOGRAPHIC DIRECTIONS. GENERALLY IT CAN BE ASSUMED THAT ONLY STRESSES IN THE PLANE OF THE DIE ARE SIGNIFICANT, SO ONLY TO AND TO ARE NON-ZERO. A TYPICAL STRAIN GAUGE BUILT INTO THE (001) SURFACE OF A CHIP WOULD APPEAR AS FOLLOWS.

Figure 1. Crystallographic orientations of the resistor rosette and the two coordinate systems.

IT CAN BE SHOWN FROM (1) THAT

$$\Delta R_A/R_A = \frac{1}{Z} \left( \widetilde{\Pi}_{i1} + \widetilde{\Pi}_{i2} \right) \left( \widetilde{\sigma}_i' + \widetilde{\sigma}_2' \right) + \left( \widetilde{\Pi}_{i1} - \widetilde{\Pi}_{i2} \right) \widetilde{C}_{i2}$$

(3A)

$$\Delta R_{B}/R_{B} = \frac{1}{2} \left( \widetilde{\Pi}_{II} + \widetilde{\Pi}_{I2} \right) \left( \overline{\sigma}_{i} + \overline{\sigma}_{2}' \right) - \left( \widetilde{\Pi}_{II} - \widetilde{\Pi}_{I2} \right) \widetilde{C}_{I2}'$$

(3B)

$$\Delta R_c/R_c = \frac{1}{2} \left( \tilde{\pi}_{11} + \tilde{\pi}_{12} + \tilde{\pi}_{44} \right) \tilde{\sigma}_1' + \frac{1}{2} \left( \tilde{\pi}_{11} + \tilde{\pi}_{12} - \tilde{\pi}_{44} \right) \tilde{\sigma}_2'$$

(3c)

$$\Delta R_D/R_D = \frac{1}{2} \left( \widetilde{\mathcal{I}}_{II} + \widetilde{\mathcal{I}}_{I2} - \widetilde{\mathcal{I}}_{44} \right) \sigma_i^{\prime} + \frac{1}{2} \left( \widetilde{\mathcal{I}}_{II} + \widetilde{\mathcal{I}}_{I2} + \widetilde{\mathcal{I}}_{44} \right) \nabla_i^{\prime}$$

(3D)

THE STRESSES (PRIMED) ARE REFERRED TO X- AND Y- AXES OF THE CHIP, WHICH LIE ALONG 110 DIRECTIONS, WHEREAS THE PIEZORESISTANCE COEFFICIENTS ARE REFERRED TO THE CUBIC AXES OF THE CRYSTAL, WHICH LIE ALONG 1000 DIRECTIONS.

SO MEASUREMENT OF THE FOUR FRACTIONAL RESISTANCE CHANGES OVERDETERMINES THE STRESSES. SO A CONSISTENCY CHECK IS AVAILABLE IN CASE RESISTANCE CHANGES ARE DUE TO EFFECTS OTHER THAN STRESS.

VALUES OF PIEZORESISTANCE COEFFICIENTS HAVE BEEN MEASURED BY MANY WORKERS (REFS. 15-20).

# **MEASUREMENT ISSUES:**

- O TYPICAL RESISTANCE CHANGES DUE TO DIE ATTACH ARE FRACTIONS OF A PERCENT, UP TO ABOUT 2 PERCENT.

- O TEMPERATURE OF BEFORE AND AFTER MEASUREMENTS MUST NOT DIFFER BY MORE THAN A DEGREE OR SO. RESISTANCE CHANGES DUE TO TEMPERATURE ARE TYPICALLY 0.2% PER DEGREE C.

- O IDENTITY MUST BE TRACKED BECAUSE THE WAFER-TO-WAFER AND ACROSS-WAFER VARIATION OF RESISTANCE CAN BE AS MUCH AS 100%.

- O A HIGH-RESOLUTION (5 1/2 DIGIT) DVM SHOULD BE USED, AND THE MEASUREMENTS SHOULD BE 4-POINT.

- O BEWARE OF RESISTANCE CHANGES DUE TO EFFECTS OTHER THAN STRESS. ESPECIALLY IF DICE SEE TEMPERATURES GREATER THAN ABOUT 440 DEG C.

### PROBLEMS:

DERIVE EQUATIONS (3) FROM EQUATION (1).

DERIVE A SIMPLE CONDITION ON  $\Delta R_A/R_A$  ETC. WHICH CHECKS THE CONSISTENCY OF EQUATIONS (3).

WHAT ARE THE PROBLEMS IN DETERMINING THE TRANSIENT STRESSES DUE TO THERMAL SHOCK USING A PIEZORESISTIVE STRAIN GAUGE?

HOW MANY SQUARES SHOULD A STRESS-SENSITIVE RESISTOR BE?

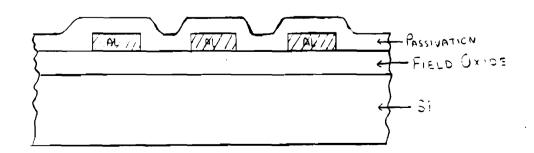

# MOISTURE SENSING ELEMENT DESIGN

# SCOPE:

- O TO DETECT THE EFFECT OF MOISTURE AND IONIC CONTAMINANTS.

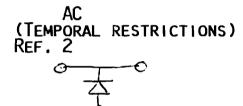

- O MEASUREMENTS CAN BE DC OR AC.

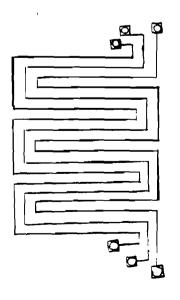

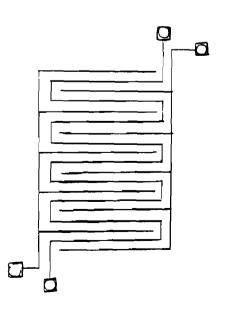

- O USE A TRIPLE TRACK FOR DC.

- O USE INTERLEAVED STRUCTURE FOR AC.

- O THE ELEMENTS CAN BE PASSIVATED OR UNPASSIVATED. WE WILL FOCUS ON PASSIVATED ELEMENTS.

- O GOOD REVIEWS OF SURFACE CONDUCTION DUE TO MOISTURE CAN BE FOUND IN REFS. 6, 7, AND 22. THIS MUST BE CONSIDERED IN DESIGN OF SENSORS.

- O SOMETIMES ADJACENT METAL TRACKS ARE USED MERELY TO DETECT CONDENSATION. THIS IS A MUCH LESS DEMANDING MEASUREMENT PROBLEM. REF. 8 IS A GOOD EXAMPLE.

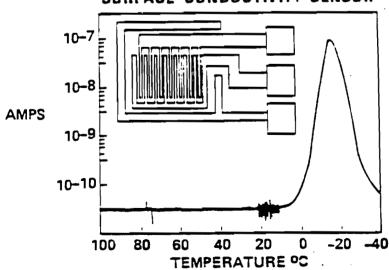

### SURFACE CONDUCTIVITY SENSOR

COMPONENTS ASSEMBLY/TEST

# DC MEASUREMENTS USING TRIPLE TRACKS:

- O SUSTAIN 100 V BETWEEN CENTER AND OUTER CONDUCTOR.

- O USE MINIMUM SPACING TO MAXIMIZE ELECTRIC FIELD (TYPICALLY CAN GET 1XE5 V/CM).

- O DESIGN SUCH THAT CURRENTS WILL BE GREATER THAN 1 PA.

- O SURFACE (OR INTERFACE) CURRENTS USUALLY DOMINATE. THAT IS,

RHO(BULK) [OHM-CM] > RHO(SURFACE) [OHM/SQUARE] X T [CM]

TYPICAL RHO(BULK) AT 23 DEG C AND E ABOUT 1XE6 V/CM (REF. 9):

| MATERIAL<br>S13N4 | DEPOSITION PROCESS                    | RHO(BULK) [OHM-CM] |

|-------------------|---------------------------------------|--------------------|

| S13N4             | PLASMA SIH4 + NH3<br>SUBST 3000 DEG C | 1.ØxE15            |

| S102              | CVD, SIH4 + 02 AT 450 D               | DEG C 3.3xE15      |

| PSG               | CVD, S1H4 + 02 + PH3<br>AT 450 DEG C  | 6.6xE16            |

TYPICAL RHO(SURFACE) AT 23 DEG C AND ABOUT 1XE5 V/CM (REF. 10):

| MATERIAL  | RELATIVE HUMIDITY (%) | RHO(SURF) [OHMS/SQ] |

|-----------|-----------------------|---------------------|

| CVD S102  | 30                    | 8.9xE16             |

| CVD \$102 | <u>50</u>             | 1.4x <u>E</u> 15    |

| CVD \$102 | 70                    | 3.5x <u>E</u> 13    |

| CVD S102  | 90                    | 2.8xE12             |

TENDS TO BE INDEPENDENT OF MATERIAL AND DEPOSITION CONDITIONS (SEE ALSO REFS 6 AND 7).

SO FOR TYPICAL PASSIVATION THICKNESSES ( $T = 1 \times E - 4 \text{ cm}$ ) THE ABOVE INEQUALITY IS USUALLY EASILY SATISFIED.

### **EXAMPLE:**

WHAT LENGTH OF 10 MICRON SPACING TRIPLE-TRACK WOULD BE NEEDED TO HAVE A SIGNAL CURRENT OF 1 PÅ AT 30 % R.H. FOR A 1 MICRON THICK PSG FILM?

SHEET RESISTIVITY DUE TO SURFACE IS 9xE16 (OHM/SQ). THE PARALLEL SHEET RESISTIVITY DUE TO THE BULK IS 7xE20 (OHM/SQ). Assume 100 Volts, so E=1xE5 V/cm. So current per unit length leaving center conductor is

$J = 2 \times E/RHO$  (SHEET) = 2 x E5 / 9xE16 = 2.2 x E-12 A/CM (FACTOR OF TWO ACCOUNTS FOR TWO CURRENT PATHS). SO REQUIRED LENGTH IS

$L = 1 \times E-12/2.2 \times E-12 = .45 \text{ cm}$

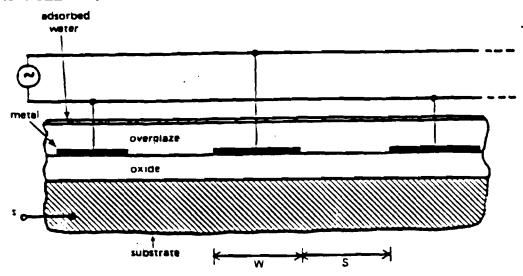

# AC MEASUREMENTS USING INTERLEAVED STRUCTURES:

- O THE BEST PRACTICAL APPROACH IS DUE TO MERRETT, SIM AND BRYANT (REF. 11).

- O THEY ALSO ASSUME THAT BULK CONDUCTION IS NEGLIGIBLE.

- O THEY ASSUME THAT THE ELEMENTS ARE PASSIVATED.

- O THERE IS NO NEED TO USE HIGH VOLTAGE.

- O THE TECHNIQUE WORKS ON REAL DEVICES, AS WELL AS ON TEST CHIPS.

- O THEY MEASURE THE CAPACITANCE, CM, BETWEEN THE TWO SETS OF TRACKS. CM IS THE SUM OF CI, THE (CONSTANT) INHERENT CAPACITANCE, AND CW, THE CAPACITANCE DUE TO WATER.

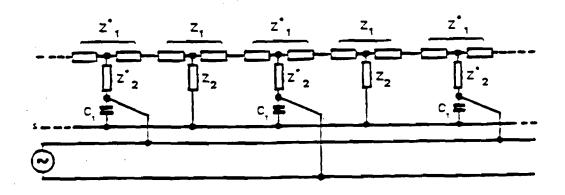

- O THE INTERLEAVED STRUCTURE CAN BE MODELED AS AN AC NETWORK AS FOLLOWS:

O AC NETWORK ANALYSIS SHOWS THAT CW IS GIVEN VIA THE CAPACITANCE RATIO

$$\frac{C_{W}}{C_{i}} = \left\{ \frac{1}{C_{t}W} \sqrt{\frac{2\sigma C_{o}}{\omega}} \right\} (1+Y)^{1/2}$$

(1)

WHICH HOLDS WHEN THE CONDITION

$$S\sqrt{\frac{\omega C_0}{2\sigma}} \ge 4 \tag{2}$$

IS SATISFIED. IN EQUATIONS (1) AND (2),

CO IS THE CAPACITANCE PER UNIT AREA BETWEEN THE CONDUCTING FILM AND THE SUBSTRATE,

CT IS THE CAPACITANCE PER UNIT AREA BETWEEN THE TRACKS AND THE SUBSTRATE,

Y IS THE THICKNESS OF THE PASSIVATION DIVIDED BY THE TOTAL THICKNESS OF THE PASSIVATION AND THE OXIDE UNDER THE TRACKS,

IS THE SHEET CONDUCTIVITY OF THE WATER FILM,

S AND W ARE, RESPECTIVELY, THE SPACING AND WIDTH OF THE INTERLEAVED ALUMINUM LINES.

- O NOTE THE FOLLOWING FEATURES

- THE SURFACE CONDUCTIVITY IS THE ONLY SURFACE-SENSITIVE PARAMETER.

- NEITHER THE SPACING, NOR THE LENGTH OF THE LINES ARE INVOLVED, SO THE EQUATION IS VALID FOR ANY METALLIZATION PATTERN.

- MOST STRUCTURES HAVE COMPARABLE VALUES OF CO, CT, Y, AND W SO THE VALUE OF THE CAPACITANCE RATIO IS PRIMARILY DEPENDENT ON THE SURFACE CONDUCTIVITY.

- THE CAPACITANCE RATIO VARIES INVERSELY AS THE SQUARE ROOT OF FREQUENCY, SO THE CONTRIBUTION ABSORBED WATER MAKES TO THE MEASURED CAPACITANCE DECREASES AS THE FREQUENCY IS INCREASED.

### O MEASUREMENT NOTES:

- A GOOD FREQUENCY TO USE IS A COMPROMISE BETWEEN MAKING (1) LARGE ENOUGH TO MEASURE, AND SATISFYING (2), A GOOD CHOICE IS 100 Hz.

- TO ISOLATE CW, MAKE TWO MEASUREMENTS: ONE AT A FREQUENCY SUFFICIENTLY HIGH TO ELIMINATE THE EFFECT OF CW, AND ONE AT 100Hz. THEN

CW/CI = [C(100Hz) - C(INFINITY)]/C(INFINITY)

### PROBLEMS:

HOW WOULD THE CAPACITANCE RATIO BE EXTRACTED IF THE HIGHEST FREQUENCY AVAILABLE COULD NOT MAKE CW NEGLIGIBLE?

WOULD A CONDUCTANCE MEASUREMENT BE MORE SUITABLE?

IS THERE AN UPPER LIMIT ON THE SPACING OF THE INTERLEAVED STRUCTURE?

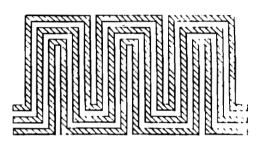

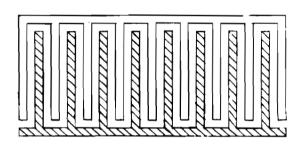

WHICH OF THE FOLLOWING STRUCTURES MAKES MORE EFFICIENT USE OF REAL-ESTATE? BY WHAT FACTOR? DOES THE MORE AREA-EFFICIENT ONE HAVE ANY DISADVANTAGES RELATIVE TO THE OTHER?

5. DESIGN GUIDELINES - REVIEW OF OBJECTIVES - GUIDELINES COMPONENTS ASSEMBLY/TEST

# 5. DESIGN GUIDELINES

### A REMINDER OF OUR OBJECTIVES:

- USE THE TEST CHIPS TO CHARACTERIZE AND QUALIFY NEW WAFER AND ASSEMBLY PROCESSES.

- EXPERIMENTS WILL INVOLVE HUNDREDS OF PIECES TO GIVE A STATISTICAL CHARACTERIZATION OF PROCESSES.

- FACTORY (UNSKILLED) ASSEMBLY SHOULD BE EASY. DESIGN RULES SHOULD BE FOLLOWED.

- USE AN AUTOMATIC PARAMETRIC TESTER WITH SOFTWARE-CONTROLLED SWITCHING MATRIX.

- BUILD A QUALITY AND RELIABILITY DATA BASE BASED ON A FEW WELL-CHARACTERIZED SENSORS.

# 5. DESIGN GUIDELINES (CONTINUED)

EXPERIENCE HAS GENERATED THE FOLLOWING DESIGN GUIDELINES:

IN ORDER OF PRIORITY...

- (A) THE DIE SIZE SHOULD BE ADJUSTABLE. IT MUST BE POSSIBLE TO SIMULATE THE DIE SIZE OF ANY PRODUCT CHIP.

- (B) THE TEST CHIP MUST OBEY WAFER FAB AND ASSEMBLY (ESPECIALLY WIRE-RELATED) DESIGN RULES.

- (C) THE TEST CHIP MUST BE TESTABLE AT THE WAFER LEVEL.

- (D) TEST CHIPS MUST HAVE VERY HIGH WAFER FAB YIELD.

- (E) A GIVEN TEST CHIP SHOULD BE MANUFACTURABLE ON ANY WAFER FAB PROCESS.

- (F) FOR TEST CHIPS THAT USE A PARAMETRIC SHIFT AS AN INDICATION (EG. STRESS MEASUREMENTS, OR THERMAL DEGRADATION) IT IS DESIRABLE TO MAINTAIN CHIP IDENTITY THROUGH ASSEMBLY WITHOUT SPECIAL ATTENTION.

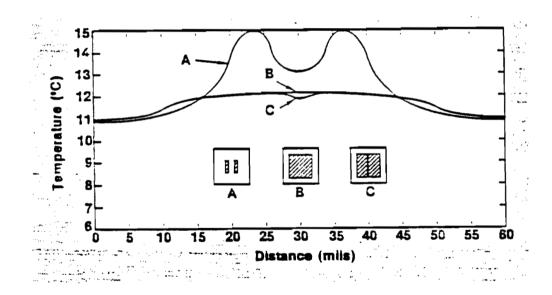

- (G) IT IS DESIRABLE TO BE ABLE TO PRODUCE A MAP OF ENVIRONMENTAL PARAMETERS ACROSS THE CHIP SURFACE.

# 6. CASE STUDIES

- THERMAL TEST CHIP

- CRACK DETECTION CHIP

- STRESS MEASUREMENT

- MOISTURE SENSING TEST CHIP

- CASE STUDY SUMMARY

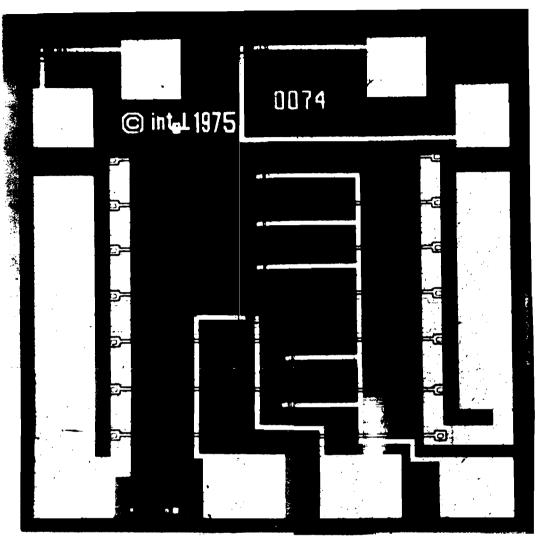

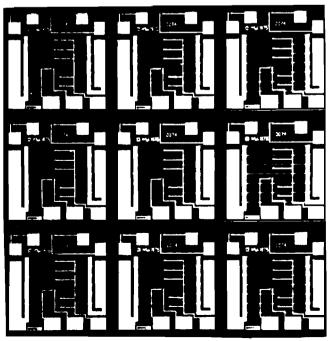

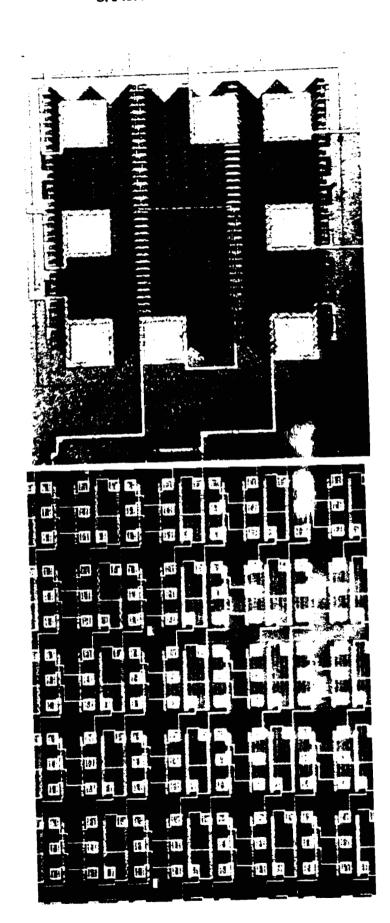

# THERMAL IMPEDANCE CHIP

# THERMAL TEST CHIP

### **FEATURES:**

- O VARIABLE DIE SIZE.

- O VARIABLE DISSIPATION AND TEMPERATURE SENSE DISTRIBUTION.

#### BUT

### PROBLEMS:

- O VARIABLE DISTRIBUTION IS ACHIEVED THROUGH WIREBOND PLACEMENT, LEADING TO DESIGN RULE VIOLATIONS:

- WIRE OVER EDGE

- ON-CHIP BONDS

#### SOLUTIONS:

- O LINK POWER RESISTORS ACROSS SCRIBE GRID.

- O LINK SENSE DIODES, OR MULTIPLEX.

### DESIGN GUIDELINE EVALUATION:

A. ADJUSTABLE DIE SIZE YES

C. OBEY DESIGN RULES ASSEMBLY NO, FAB YES.

C. WAFER TESTABLE YES

D. HIGH FAB YIELD YES

E. ANY FAB PROCESS YES

F. ELECTRICAL ID NO

G. DIE SURFACE MAPS CRUDE

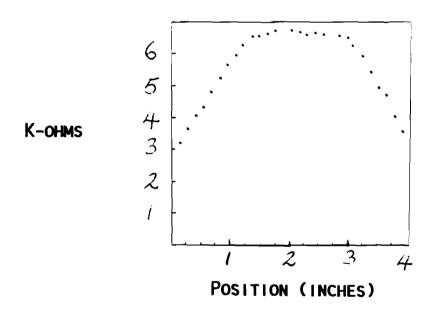

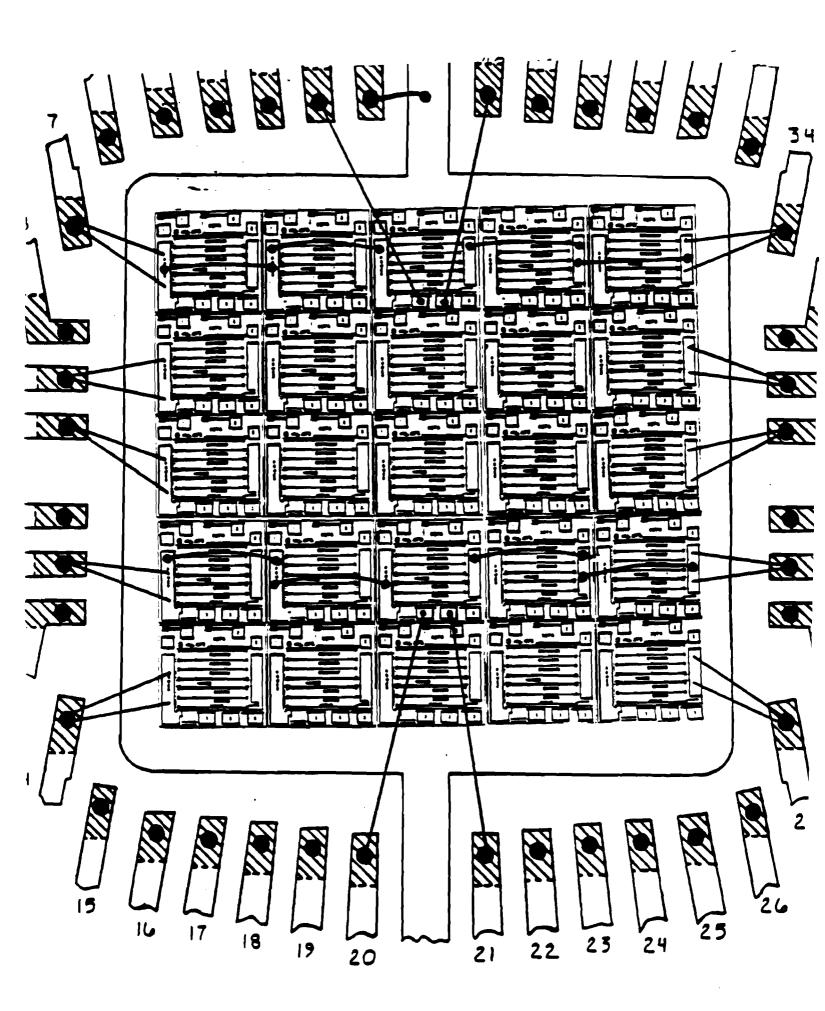

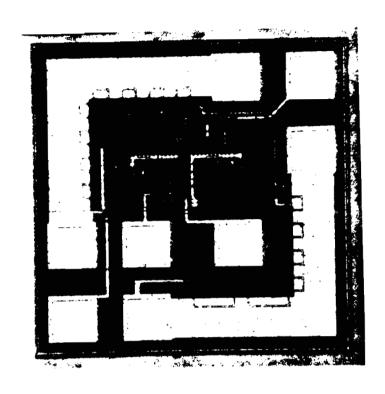

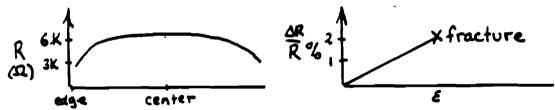

# CRACK DETECTION CHIP

#### **FEATURES:**

- O ELECTRICAL MAPPING OF DIE CRACKS DUE TO DIE ATTACH OR WIREBOND.

- O JUNCTIONS SENSITIVE TO THERMAL HISTORY.

- O DIE-OFF DETECTION.

### PROBLEMS:

- O HARD TO TEST AT THE WAFER LEVEL.

- O RESISTORS TOO HIGH IN VALUE (ABOUT 4K OHM).

- O BOND PADS VIOLATE DESIGN RULES (ALUMINUM OVER POLYSILICON).

### SOLUTIONS:

- O PUT FUSES IN SCRIBE LINES.

- O FATTEN UP RESISTORS.

- O USE DIFFERENT SENSORS UNDER BOND PADS TO DETECT FRACTURE DUE TO WIRE BONDING.

### DESIGN GUIDELINE EVALUATION:

- A. ADJUSTABLE DIE SIZE? YES

- B. OBEY DESIGN RULES? ASSEMBLY YES, FAB NO

- C. WAFER TESTABLE? NO

- D. HIGH FAB YIELD YES

- E. ANY FAB PROCESS YES

- F. ELECTRICAL ID NO

- G. DIE SURFACE MAPS YES

# STRESS MEASUREMENT CHIP

# STRESS MEASUREMENT

### **FEATURES:**

- O FOUR-RESISTOR, FOUR POINT STRAIN ROSETTE.

- O FAB DESIGN VARIATION.

- O DIODES FOR TEMPERATURE MEASUREMENT.

- O PARAMETRIC MEASUREMENTS.

#### PROBLEMS:

O LARGE NUMBER OF PADS PER SUBDIE. LEADS TO AWKWARD PAD LOCATIONS AND WIRE BOND DESIGN RULE VIOLATIONS.

O PROCESS VARIATIONS ACROSS WAFER OF STRAIN GAUGE RESISTORS ARE GREATER THAN THE PARAMETRIC SHIFTS TO BE DETECTED. HENCE MANUAL IDENTITY TRACKING IS NECESSARY.

O PRODUCING ONE VARIANT IS DIFFICULT - EITHER WASTE SILICON, DO VISUAL SORTING, OR DO COMPLICATED MULTI-PASS SAWING.

O MANY SENSORS CANNOT BE REACHED BY WIRES. MAPPING PARAMETERS ACROSS THE DIE IS PRACTICALLY IMPOSSIBLE.

#### SOLUTIONS:

- O MAKE SUBDIE LARGER AND PUT PADS ONLY ON ITS PERIPHERY.

- O MAKE PROVISION FOR ELECTRICAL DIE IDENTITY.

- O MAKE EACH SUBDIE IDENTICAL. ALL FUNCTIONS ON EACH DIE.

- O LOCAL AMPLIFICATION OF SIGNALS, MULTIPLEX TO PERIPHERY VIA CONNECTIONS ACROSS SCRIBE LINES.

## STRESS MEASUREMENT (CONTINUED)

### DESIGN GUIDELINE EVALUATION:

A. ADJUSTABLE DIE SIZE? YES(?)

B. OBEY DESIGN RULES? ASSEMBLY NO, FAB YES

C. WAFER TESTABLE? YES

D. HIGH FAB YIELD YES

E. ANY FAB PROCESS YES

F. ELECTRICAL ID VARIANT ONLY

G. DIE SURFACE MAPS NO

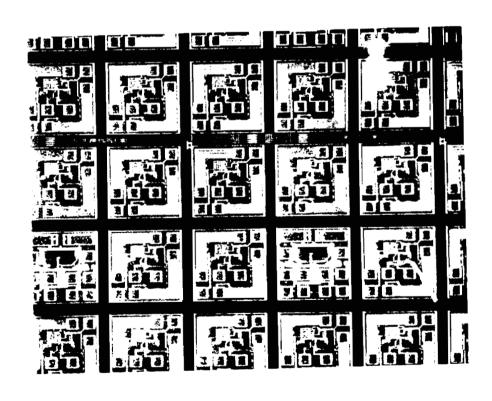

# MOISTURE/CORROSION SENSING CHIP

### MOISTURE SENSING TEST CHIP

### **FEATURES:**

- O SIMULATES A SPECIFIC CHIP (16K DRAM).

- O HAS 12 VARIANTS WITH VARIOUS MOISTURE-SENSITIVE STRUCTURES.

- O PROVISION FOR ELECTRICAL IDENTIFICATION OF VARIANT.

- O SENSORS USED ARE TRIPLE TRACKS AND MOS CAPACITORS.

#### PROBLEMS:

- O SPECIFIC TO ONE TYPE OF CHIP.

- O DIE SIZE TOO LARGE (180 X 90 MILS) TO USE AS MODULE IN "ADJUSTABLE" CHIP.

- O TOO MANY VARIANTS ON ONE WAFER.

#### SOLUTION:

O A COMPLETELY DIFFERENT DESIGN IS NEEDED TO IMPLEMENT THE SENSORS IN OUR METHODOLOGY.

#### DESIGN GUIDELINE EVALUATION:

A. ADJUSTABLE DIE SIZE? NO

B. OBEY DESIGN RULES? ASSEMBLY YES, FAB YES

C. WAFER TESTABLE? YES

D. HIGH FAB YIELD YES

E. ANY FAB PROCESS YES

F. ELECTRICAL ID No.

G. DIE SURFACE MAPS YES

# CASE STUDY SUMMARY

| GUIDELINE              | THERMAL | CRACK | STRESS  | MOISTURE |

|------------------------|---------|-------|---------|----------|

| A. ADJUSTABLE DIE SIZE | YES     | YES   | YES(?)  | No       |

| B. OBEYS DESIGN RULES  |         |       |         |          |

| - ASSEMBLY             | No      | YES   | No      | YES      |

| - FAB                  | YES     | No    | YES     | YES      |

| C. WAFER TESTABLE      | YES     | No    | YES     | YES      |

| D. HIGH FAB YIELD      | YES     | YES   | YES     | YES      |

| E. ANY FAB PROCESS     | YES     | YES   | YES     | YES      |

| F. ELECTRICAL ID       | No      | No    | VARIANT | VARIANT  |

| G. DIE SURFACE MAPS    | CRUDE   | YES   | No      | YES      |

THE PRIMARY CHALLENGE IS TO PUT YES IN ALL OF THE FIRST THREE GUIDELINES

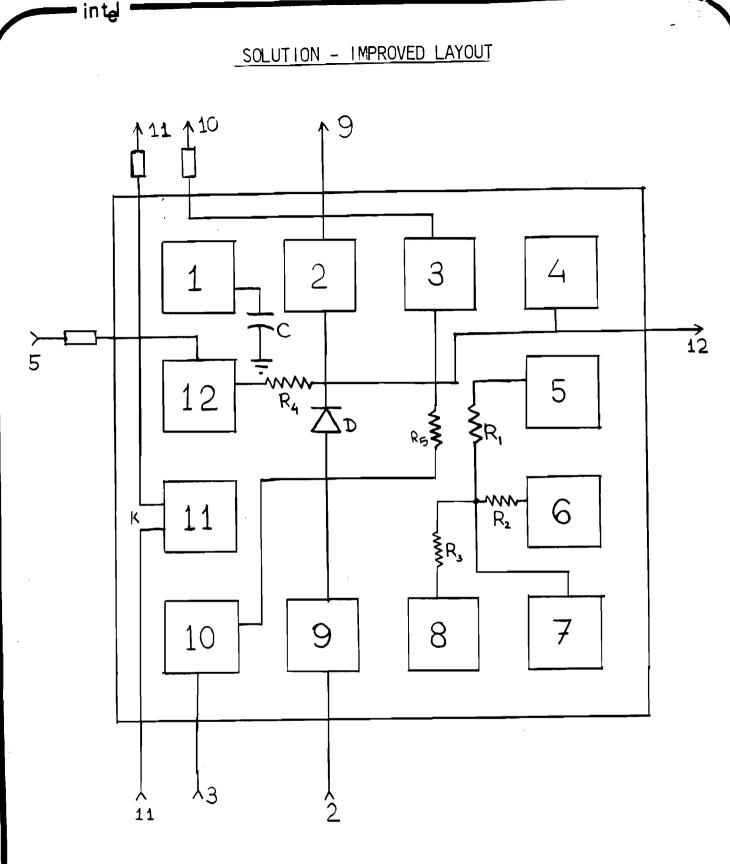

### 7. DESIGN SOLUTIONS

- O WE NEED TO SATISFY THE FOLLOWING SIMULTANEOUSLY:

- A. ADJUSTABLE DIE SIZE

- B. OBEY DESIGN RULES.

- C. CHIPS TESTABLE AT THE WAFER LEVEL

HOW DO WE DO IT?

- O BONDING PAD PLACEMENT.

- o Problem

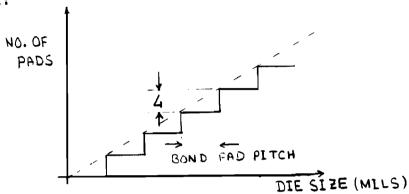

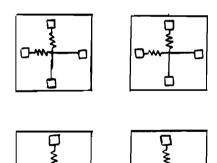

# A. DIE SIZE SHOULD BE ADJUSTABLE

O KEY QUESTION: HOW LARGE SHOULD THE MODULES BE?

O SMALL MODULES ALLOW GOOD SIZE FLEXIBILITY BUT LIMIT THE NUMBER OF BOND PADS, AND REAL-ESTATE FOR SENSORS, PER MODULE.

O LARGE MODULES LIMIT SIZE FLEXIBILITY.

O MODULAR CHIPS TEND TO LEAD TO WIRE-RELATED DESIGN RULE PROBLEMS.

o Example:

IS THERE ANY ADVANTAGE TO MAKING THE MODULES RECTANGULAR?

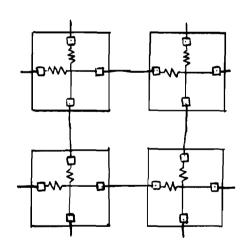

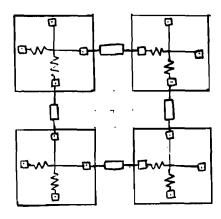

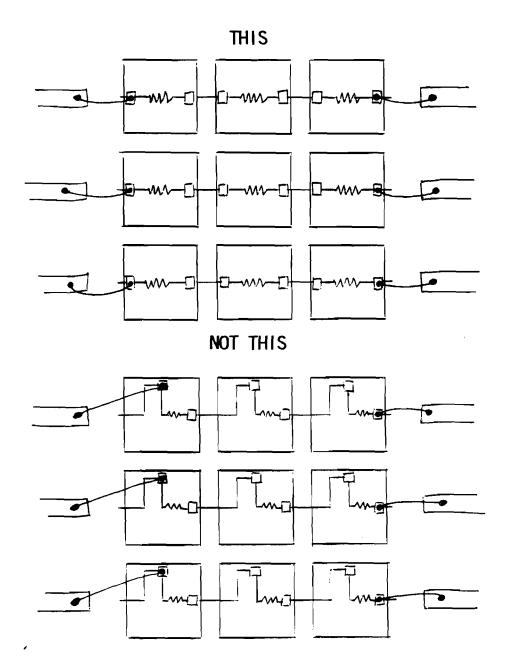

### B. WAFER FAB AND ASSEMBLY DESIGN RULES MUST BE OBEYED

O THE CHIPS MUST "LOOK" LIKE PRODUCT CHIPS IN FAB AND IN ASSEMBLY.

O FOR MODULAR CHIPS, THE MOST DIFFICULT DESIGN RULES TO OBEY ARE WIRE-RELATED DESIGN RULES.

O THE SOLUTION IS TO INTERCONNECT MODULES ACROSS SCRIBE LINES.

O INTERCONNECTION ACROSS SCRIBE LINES LEADS TO TESTABILITY PROBLEMS AT THE WAFER LEVEL.

### C. CHIPS MUST BE TESTABLE AT THE WAFER LEVEL

O TESTABILITY AT THE WAFER LEVEL IS CRITICAL TO CHARACTERIZATIONS WHICH SEEK INFORMATION ABOUT THE EFFECT OF ASSEMBLY ON CHIPS. NOT SO IMPORTANT FOR STUDIES OF THE EFFECT OF ENVIRONMENT ON PACKAGED CHIPS.

O TEST CHIPS COMPRISING SEVERAL MODULES MUST BE ELECTRICALLY ISOLATED FROM EACH OTHER BEFORE TESTING.

O USE FUSES IN SCRIBE LINES AND DO A DOUBLE PROBE PASS. THE FIRST PASS WILL BLOW FUSES IN THE APPROPRIATE SCRIBE LINES, AND THE SECOND PASS WILL ELECTRICALLY TEST (AND INK) THE ELECTRICALLY ISOLATED TEST CHIPS.

O FOR SOME APPLICATIONS POLYSILICON FUSES HAVE UNACCEPTABLY HIGH RESISTANCE.

## BONDING PAD PLACEMENT

O DISTRIBUTED SENSORS (INTERCONNECTED BETWEEN MODULES): PADS MUST BE ON OPPOSITE EDGES OF THE MODULE. FOR EXAMPLE:

O LOCAL SENSORS (NOT INTERCONNECTED BETWEEN MODULES, ACCESSIBLE ONLY IN MODULES ON THE CHIP PERIPHERY): ACCESSIBILITY RULES ARE...

| No. PADS<br>PER SENSOR | PAD LOCATION<br>ON MODULE | WIRE ACCESS TO CHIP |

|------------------------|---------------------------|---------------------|

| 1                      | CORNER                    | 2 EDGES             |

| 2                      | BOTH SAME SIDE            | 1 EDGE              |

| 2                      | ADJACENT SIDES            | 1 CORNER            |

| 2                      | OPPOSITE SIDES            | NOT ACCESSIBLE      |

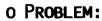

O A PROBLEM IS THE BEST WAY TO ILLUSTRATE THESE RULES...

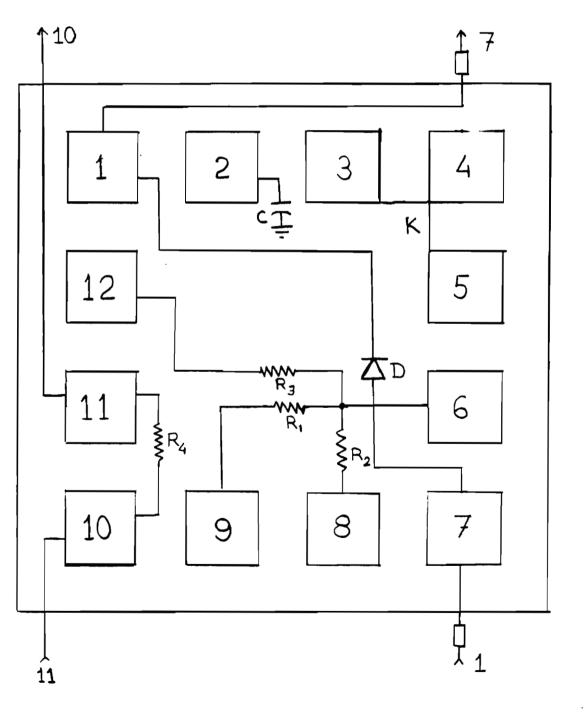

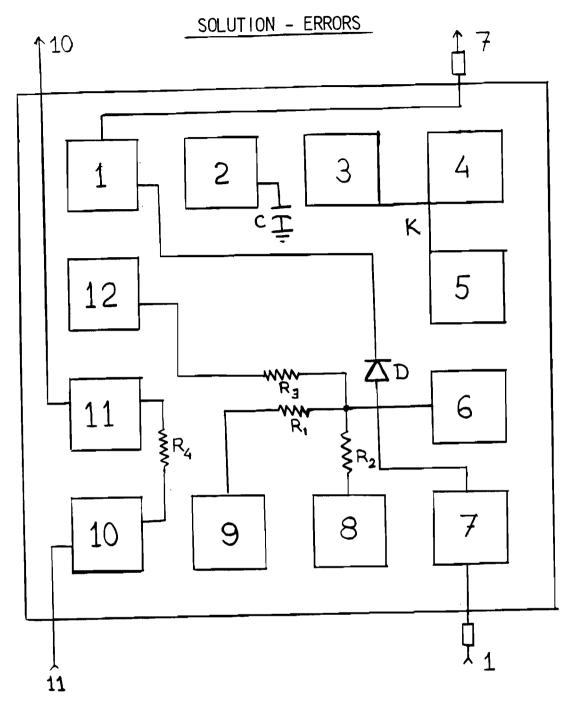

### PROBLEM

YOU ARE AN ASSEMBLY ENGINEER WITH THE JOB OF DESIGNING A MODULAR TEST CHIP. YOUR BOSS INSISTS THAT YOU SEEK THE ADVICE OF THE EXPERTS - THE LOCAL VLSI DESIGNERS. YOU'VE NEVER YET SEEN A DESIGN PRODUCED BY THOSE GUYS WHICH TOOK ACCOUNT OF ASSEMBLY DESIGN RULES. SO YOU'RE NOT TOO OPTIMISTIC. STILL, TO DEMONSTRATE THE GOOD ATTITUDE YOU DON'T REALLY HAVE, YOU GO ALONG WITH YOUR BOSS. WEEKS LATER THE VLSI DESIGNERS PRODUCE A DESIGN WITH THE FOLLOWING SCHEMATIC. YOUR MOUTH WATERS. HERE'S YOUR CHANCE TO SHOW THOSE HOT-SHOTS (AND YOUR BOSS) A THING OR TWO. POINT OUT THE ERRORS IN THE SCHEMATIC, AND PRODUCE A CORRECTED VERSION.

### 8. BIBLIOGRAPHY

- 1. F.F. OETTINGER, "THERMAL EVALUATION OF VLSI PACKAGES USING TEST CHIPS A CRITICAL REVIEW," SOLID STATE TECHNOLOGY, FEBRUARY, 1984, PP169-179

- 2. "THERMAL RESISTANCE MEASUREMENTS OF CONDUCTION-COOLED POWER TRANSISTORS," EIA RECOMMENDED STANDARD RS-313-B, OCT 1975 (ELECTRONIC INDUSTRIES ASSOCIATION, WASHINGTON, D.C.)

- 3. "SEMI SPECIFICATION: UNENCAPSULATED THERMAL TEST CHIP" (DRAFT) SEMICONDUCTOR EQUIPMENT AND MATERIALS INSTITUTE, INC., DOCUMENT NO. 1324, REV. B, JULY 26, 1985.

- 4. "ACCEPTED PRACTICES FOR MAKING MICROELECTRONIC DEVICE THERMAL CHARACTERISTICS TEST A USERS GUIDE," JEDEC ENGINEERING BULLETIN No. 20, Jan 1975 (ELECTRONIC INDUSTRIES ASSOCIATION, WASHINGTON, D.C.)

- 5. C.G. SHIRLEY, "STEADY-STATE TEMPERATURE PROFILES IN NARROW THIN-FILM CONDUCTORS," J. APPL. Phys. Vol. 57, PP777-784 (1985)

- 6. K. KAWASAKI AND N. HACKERMAN, "ON THE VARIATION OF SURFACE CONDUCTION CURRENT OF POROUS VYCOR GLASS BY THE ADSORBTION OF WATER VAPOR", SURFACE SCIENCE, Vol. 10, pp299-302 (1968).

- 7. N. L. SBAR AND R. P. KOZAKIEWICZ, "NEW ACCELERATION FACTORS FOR TEMPERATURE, HUMIDITY, BIAS TESTING", IEEE TRANS. ON ELECTRON DEV., Vol. ED-26 pp56-71 (1979).

- 8. R.K. LOWRY, L.A. MILLER, A.W. JONAS, AND J.M. BIRD, "CHARACTERISTICS OF A SURFACE CONDUCTIVITY MOISTURE MONITOR FOR HERMETIC INTEGRATED CIRCUIT PACKAGES," PROCEEDINGS OF 17TH INTERNATIONAL RELIABILITY PHYSICS SYMPOSIUM, PP97-102 (1979).

- 9. R.B. COMIZZOLI, "SURFACE AND BULK ELECTRICAL CONDUCTION IN LOW-DEPOSITION TEMPERATURE SI3N4 AND AL203 FILMS FOR SILICON DEVICES," RCA REVIEW, Vol. 37, PP473-482 (1976)

- 10. R.B. COMIZZOLI, "BULK AND SURFACE CONDUCTION IN CVD S102 AND PSG PASSIVATION LAYERS", J. ELECTROCHEM. Soc., Vol. 123, PP386-391 (1976).

- 11. R.P. MERRETT, S.P. SIM, AND J.P. BRYANT, "A SIMPLE METHOD OF USING THE DIE OF AN INTEGRATED CIRCUIT TO MEASURE THE RELATIVE HUMIDITY INSIDE ITS ENCAPSULATION," PROCEEDINGS OF 18TH INTERNATIONAL RELIABILITY PHYSICS SYMPOSIUM, PP17-25 (1980).

- 12. R.C. BLISH, II AND L. PAROBEK, "WIRE BOND INTEGRITY TEST CHIP", 21ST ANNUAL PROCEEDINGS, INTERNATIONAL RELIABILITY PHYSICS SYMPOSIUM (1983).

- 13. P. M. HALL, "RESISTANCE CALCULATIONS FOR THIN FILM PATTERNS", THIN SOLID FILMS, Vol. 1, PP277-295 (1967/1968)

- 14. Y. KANDA, "A GRAPHICAL REPRESENTATION OF THE PIEZORESISTANCE COEFFICIENTS OF SILICON," IEEE TRANS. ON ELECTRON DEVICES, Vol. ED-29, PP64-70 (1982).

- 15. O.N. TUFTE AND E.L. STELZER, "PIEZORESISTIVE PROPERTIES OF SILICON DIFFUSED LAYERS," J. APPL. PHYS., Vol. 34, PP313-318 (1963).

- 16. C.S. SMITH, "PIEZORESISTANCE EFFECT IN GERMANIUM AND SILICON," PHYS. REV., Vol. 94, PP42-49 (1954).

- 17. F. J. MORIN, T.H. GEBALLE, C. HERVING, "TEMPERATURE DEPENDENCE OF THE PIEZORESISANCE OF HIGH-PURITY SILICON AND GERMANIUM," PHYS. Rev., Vol. 105, PP525-539 (1957).

- 18. R.W. KEYS, "THE EFFECTS OF ELASTIC DEFORMATION ON THE ELECTRICAL CONDUCTIVITY OF SEMICONDUCTORS," SOLID-STATE PHYSICS, Vol. 11, PP140-221, 1960.

- 19. O.R. KERR AND A.G. MILNES, "PIEZORESISTANCE OF DIFFUSED LAYERS IN CUBIC SEMICONDUCTORS," J. APPL. PHYS., VOL. 34, PP727-732 (1963).

- 20. S. S. SHAKHIDZHANOV, "TOTAL PIEZORESISTANCE TENSOR OF P-TYPE SILICON IN A WIDE TEMPERATURE RANGE," SOV.-PHYS.-SEMICOND., Vol. 11, PP586-587 (1977).

- 21. M. IGASAWA, Y. IWASAKI, T. SUTOH, "DEFORMATION OF ALUMINUM METALIZATION IN PLASTIC-ENCAPSULATED SEMICONDUCTOR DEVICES CAUSED BY THERMAL SHOCK," 18TH ANNUAL PROCEEDINGS INTERNATIONAL RELIABILITY PHYSICS SYMPOSIUM, PP171-177 (1980).

- 22. S. P. SIM AND R. W. LAWSON, "THE INFLUENCE OF PLASTIC ENCAPSULANTS AND PASSIVATION LAYERS ON THE CORROSION OF THIN ALUMINUM FILMS SUBJECTED TO HUMIDITY STRESS," 17TH ANNUAL RELIABILITY PHYSICS SYMPOSIUM, PP103-112 (1979).

K: ACCESS AT CORNERS ONLY. USES THREE PAD PER DIE.

R3: NOT ACCESSIBLE.

R1, R2: ACCESSIBLE AT ONE CORNER ONLY.

$\mbox{R4}$  : Does not use opposite edges. Not testable on wafer (no fuses). Wastes a corner PAD.

D: USES CORNER PADS. SHOULD NOT USE FUSES.

C: SHOULD BE ON A CORNER TO ALLOW ACCESS FROM TWO EDGES.

DISTRIBUTING K FROM MODULE TO MODULE FREES UP TWO PADS. IT ALSO MAKES IT UNNECESSARY TO USE THREE PADS ON THE SAME EDGE (A VERY RESTRICTING REQUIREMENT). TWO EXTRA PADS ALLOWS THE ADDITION OF ANOTHER CRACK-DETECTION RESISTOR.